# AirPrime HL7800 and HL7800-M

# **Product Technical Specification**

41111094 7 October 04, 2019

## **Important Notice**

Due to the nature of wireless communications, transmission and reception of data can never be guaranteed. Data may be delayed, corrupted (i.e., have errors) or be totally lost. Although significant delays or losses of data are rare when wireless devices such as the Sierra Wireless modem are used in a normal manner with a well-constructed network, the Sierra Wireless modem should not be used in situations where failure to transmit or receive data could result in damage of any kind to the user or any other party, including but not limited to personal injury, death, or loss of property. Sierra Wireless accepts no responsibility for damages of any kind resulting from delays or errors in data transmitted or received using the Sierra Wireless modem, or for failure of the Sierra Wireless modem to transmit or receive such data.

## Safety and Hazards

Do not operate the Sierra Wireless modem in areas where cellular modems are not advised without proper device certifications. These areas include environments where cellular radio can interfere such as explosive atmospheres, medical equipment, or any other equipment which may be susceptible to any form of radio interference. The Sierra Wireless modem can transmit signals that could interfere with this equipment. Do not operate the Sierra Wireless modem in any aircraft, whether the aircraft is on the ground or in flight. In aircraft, the Sierra Wireless modem **MUST BE POWERED OFF**. When operating, the Sierra Wireless modem can transmit signals that could interfere with various onboard systems.

Note:

Some airlines may permit the use of cellular phones while the aircraft is on the ground and the door is open. Sierra Wireless modems may be used at this time.

The driver or operator of any vehicle should not operate the Sierra Wireless modem while in control of a vehicle. Doing so will detract from the driver or operator's control and operation of that vehicle. In some states and provinces, operating such communications devices while in control of a vehicle is an offence.

## **Limitations of Liability**

This manual is provided "as is". Sierra Wireless makes no warranties of any kind, either expressed or implied, including any implied warranties of merchantability, fitness for a particular purpose, or noninfringement. The recipient of the manual shall endorse all risks arising from its use.

The information in this manual is subject to change without notice and does not represent a commitment on the part of Sierra Wireless. SIERRA WIRELESS AND ITS AFFILIATES SPECIFICALLY DISCLAIM LIABILITY FOR ANY AND ALL DIRECT, INDIRECT, SPECIAL, GENERAL, INCIDENTAL, CONSEQUENTIAL, PUNITIVE OR EXEMPLARY DAMAGES INCLUDING, BUT NOT LIMITED TO, LOSS OF PROFITS OR REVENUE OR ANTICIPATED PROFITS OR REVENUE ARISING OUT OF THE USE OR INABILITY TO USE ANY SIERRA WIRELESS PRODUCT, EVEN IF SIERRA WIRELESS AND/OR ITS AFFILIATES HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR THEY ARE FORESEEABLE OR FOR CLAIMS BY ANY THIRD PARTY.

Notwithstanding the foregoing, in no event shall Sierra Wireless and/or its affiliates aggregate liability arising under or in connection with the Sierra Wireless product, regardless of the number of events, occurrences, or claims giving rise to liability, be in excess of the price paid by the purchaser for the Sierra Wireless product.

#### **Patents**

This product may contain technology developed by or for Sierra Wireless Inc.

This product is manufactured or sold by Sierra Wireless Inc. or its affiliates under one or more patents licensed from MMP Portfolio Licensing.

# Copyright

© 2019 Sierra Wireless. All rights reserved.

#### **Trademarks**

Sierra Wireless<sup>®</sup>, AirPrime<sup>®</sup>, AirLink<sup>®</sup>, AirVantage<sup>®</sup>, WISMO<sup>®</sup>, ALEOS<sup>®</sup> and the Sierra Wireless and Open AT logos are registered trademarks of Sierra Wireless, Inc. or one of its subsidiaries.

Watcher® is a registered trademark of NETGEAR, Inc., used under license.

Windows<sup>®</sup> and Windows Vista<sup>®</sup> are registered trademarks of Microsoft Corporation.

Macintosh® and Mac OS X® are registered trademarks of Apple Inc., registered in the U.S. and other countries.

QUALCOMM® is a registered trademark of QUALCOMM Incorporated. Used under license.

Other trademarks are the property of their respective owners.

## **Contact Information**

| Sales information and technical support, including warranty and returns | Web: sierrawireless.com/company/contact-us/<br>Global toll-free number: 1-877-687-7795<br>6:00 am to 5:00 pm PST |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Corporate and product information                                       | Web: sierrawireless.com                                                                                          |

# **Document History**

| Version | Date              | Updates                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0     | November 24, 2017 | Creation                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 1.1     | February 01, 2018 | Added 3.3 Power Consumption States  Updated:  Table 2 General Features  Table 5 Pin Definition  3.2 Current Consumption  3.16 Debug Interface  3.19.3 Rx Sensitivity                                                                                                                                                                                         |  |  |

| 1.2     | May 04, 2018      | Added:  • 7.1 Japan Radio and Telecom Approval  • Table 9 Maximum Current Consumption  Updated:  • GNSS to GPS  • 1.7 ESD Specifications  • 1.8.5 RoHS Directive Compliance  • 3.2 Current Consumption  • Table 23 Digital I/O Electrical Characteristics  • 3.11 Power On Signal (PWR_ON_N)  • 3.19 RF Interface  • 6 Reliability Specification             |  |  |

| 1.3     | July 05, 2018     | Added 1.8.3 ATEX Compliance  Updated:  Table 1 Supported Bands/Connectivity  Table 2 General Features  1.5 Interfaces  Table 5 Pin Definition  Table 9 Maximum Current Consumption  3.2 Current Consumption  3.3 Power Consumption States  3.11 Power On Signal (PWR_ON_N)  3.12 Reset Signal (RESET_IN_N)  Table 43 Typical Conducted Cat-M1 RX Sensitivity |  |  |

| 1.4     | July 10, 2018     | Updated Table 10 Low Current Consumption Mode                                                                                                                                                                                                                                                                                                                |  |  |

| 1.5     | July 25, 2018     | Added:  1.8.2 Frequency Drift Correction  7 Legal Information  HL7800-M  Updated:  Table 9 Maximum Current Consumption  Moved Japan Approval to 7.1; updated Figure 25 Sample Japan Certification Indication                                                                                                                                                 |  |  |

| 1.6     | August 10, 2018   | Updated  • 7.3 FCC Statement  • 7.4 IC Statement                                                                                                                                                                                                                                                                                                             |  |  |

| Version | Date               | Updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2.0     | September 10, 2018 | Added 7.3.4 Antenna Installation  Updated:  Table 1 Supported Bands/Connectivity  1.7 ESD Specifications Table 5 Pin Definition Table 9 Maximum Current Consumption Table 17 VGPIO Electrical Characteristics Table 22 USB Electrical Characteristics Table 23 Digital I/O Electrical Characteristics Table 24 GPIO Pin Description Table 25 UART1 Pin Description Table 31 RESET_IN_N Electrical Characteristics                                                                                                           |  |  |

| 3.0     | November 12, 2018  | Added 3.3.3 Digital I/O during Hibernate Power Mode  Updated:  Table 5 Pin Definition  3.2 Current Consumption  3.3.1.2 Extended DRX (eDRX)  3.3.2 Power Modes  Table 17 VGPIO Electrical Characteristics  Table 20 USIM1 Electrical Characteristics  Table 23 Digital I/O Electrical Characteristics  3.10 Main Serial Link (UART1)  3.11 Power On Signal (PWR_ON_N)  3.12 Reset Signal (RESET_IN_N)  3.16 Debug Interfaces  Table 38 WAKE_UP Electrical Characteristics  Table 43 Typical Conducted Cat-M1 RX Sensitivity |  |  |

| 3.1     | November 13, 2018  | Updated 3.2 Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 4.0     | March 08, 2019     | Added 5 Design Guidelines  Updated:  Number of GPIOs from 11 to 12  Table 1 Supported Bands/Connectivity  Table 2 General Features  1.7 ESD Specifications  1.8.4 Regulatory  Table 5 Pin Definition  3 Detailed Interface Specifications                                                                                                                                                                                                                                                                                   |  |  |

| 4.1     | March 13, 2019     | Updated 3.8 Electrical Information for Digital I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 4.2     | March 22, 2019     | Added Table 44 Typical Conducted NB1 RX Sensitivity  Updated:  • 3.2 Current Consumption  • 3.3.1.1 Power Saving Mode (PSM)                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 4.3     | April 04, 2019     | Updated 3.2 Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 5.0     | May 08, 2019       | Added:  VBATT_PA_EN (pin 41)  3.21 External RF Voltage Control Indicator  7.2 Korean Approval                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Version | Date             | Updates                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5.0     | May 08, 2019     | Updated:  • 3.2 Current Consumption  • 3.3.2 Power Modes  • 3.7 USB Interface  • 3.10 Main Serial Link (UART1)  • Table 29 PWR_ON_N Managed Timing  • Table 33 ADC Electrical Characteristics                                                                                                                                                                                                                      |  |  |

| 6.0     | August 06, 2019  | Updated IO state in:                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 7       | October 03, 2019 | Updated 3.3.1 3GPP Power Saving Features  ADCs, Clock Interface, PWR_ON_N now available Updated Pin Definition table (pre/post reset state; power supply domain) - pins C11, C24-C29, C44 Updated 3.4 VGPIO Updated Table 29 PWR_ON_N Managed Timing Updated Table 31 RESET_IN_N Electrical Characteristics Updated 3.20 TX Indictor (TX_ON) Updated Table 50 GPS Performance Updated Figure 24 Antenna Connection |  |  |

# ->> Contents

| 1. | INTRO | 13                                             |    |

|----|-------|------------------------------------------------|----|

|    | 1.1.  | Common Flexible Form Factor (CF <sup>3</sup> ) | 14 |

|    | 1.2.  | Physical Dimensions                            | 14 |

|    | 1.3.  | General Features                               | 14 |

|    | 1.4.  | Architecture                                   | 16 |

|    | 1.5.  | Interfaces                                     | 17 |

|    | 1.6.  | Connection Interface                           | 17 |

|    | 1.7.  | ESD Specifications                             | 18 |

|    | 1.8.  | Environmental and Certifications               | 18 |

|    | 1.8   | 8.1. Environmental Specifications              | 18 |

|    | 1.8   | 3.2. Frequency Drift Correction                | 19 |

|    | 1.8   | 3.3. ATEX Compliance                           | 19 |

|    | 1.8   | 3                                              |    |

|    | 1.8   | '                                              |    |

|    | 1.8   | 3.6. Disposing of the Product                  | 20 |

|    | 1.9.  | References                                     | 20 |

| 2. | PAD [ | DEFINITION                                     | 21 |

|    | 2.1.  | Pin Types                                      | 25 |

|    | 2.2.  | Pad Configuration (Top View, Through Module)   | 26 |

| 3. | DETA  | ILED INTERFACE SPECIFICATIONS                  | 27 |

|    | 3.1.  | Power Supply                                   | 27 |

|    | 3.2.  | Current Consumption                            | 28 |

|    | 3.3.  | Power Consumption States                       | 31 |

|    | 3.3   | ·                                              |    |

|    | 3.3   | 3.2. Power Modes                               | 35 |

|    | 3.3   | 3.3. Digital I/O during Hibernate Power Mode   | 36 |

|    | 3.4.  | VGPIO                                          | 38 |

|    | 3.5.  | Real Time Clock (BAT_RTC)                      | 39 |

|    | 3.6.  | USIM Interface                                 | 40 |

|    | 3.6   | 6.1. UIM1_DET                                  | 41 |

|    | 3.7.  | USB Interface                                  | 41 |

|    | 3.8.  | Electrical Information for Digital I/O         | 41 |

|    | 3.9.  | General Purpose Input/Output (GPIO)            | 42 |

|    | 3.10. | Main Serial Link (UART1)                       | 43 |

|    | 3.1   | 0.1. 8-wire Application                        |    |

|    | 3.1   | 0.2. 4-wire Application                        | 44 |

|    | 3.1   | 0.3. 2-wire Application                        | 44 |

|    |       | 2 m 3 , pp season                              |    |

|    | 3.11. | Power On Signal (PWR_ON_N)                     | 45 |

|    | 3.1   | 11.2. PWR_ON_N Managed                                                      | 46 |

|----|-------|-----------------------------------------------------------------------------|----|

|    | 3.12. | Reset Signal (RESET_IN_N)                                                   | 47 |

|    | 3.13. | Analog to Digital Converter (ADC)                                           | 48 |

|    | 3.14. | Clock Interface                                                             | 49 |

|    | 3.15. | PCM                                                                         | 49 |

|    | 3.16. | Debug Interfaces                                                            | 49 |

|    | 3.1   | 16.1. Command Line Interface (CLI)                                          |    |

|    | 3.1   | 16.2. Modem Logs interface                                                  |    |

|    | 3.17. | Wake Up Signal (WAKE_UP)                                                    |    |

|    | 3.18. | Fast Shutdown Signal (FAST_SHUTDOWN_N)                                      |    |

|    | 3.19. | RF Interface                                                                |    |

|    |       | 19.1. RF Connection                                                         |    |

|    | ٠.    | 19.2. Maximum Output Power                                                  |    |

|    | 3.20. | TX Indicator (TX_ON)                                                        |    |

|    | 3.21. | External RF Voltage Control Indicator                                       |    |

|    | 3.21. | GPS Interface                                                               |    |

|    | 0.22. | 22.1. GPS Performance                                                       |    |

|    | 0.2   | 22.2. GPS Antenna Indicator (EXT_LNA_GPS_EN)                                |    |

| 4  | MECI  | HANICAL DRAWINGS                                                            | 56 |

|    |       |                                                                             |    |

| Э. |       | GN GUIDELINES                                                               |    |

|    | 5.1.  | Power Supply Design                                                         |    |

|    | 5.2.  | Power Cycle                                                                 |    |

|    | 5.3.  | ESD Guidelines for USIM                                                     |    |

|    | 5.4.  | ESD Guidelines for USB                                                      |    |

|    | 5.5.  | Radio Frequency Integration                                                 | 61 |

| 6. | RELI  | ABILITY SPECIFICATION                                                       | 62 |

|    | 6.1.  | Preconditioning Test                                                        | 62 |

|    | 6.2.  | Performance Test                                                            | 62 |

|    | 6.3.  | Aging Tests                                                                 | 63 |

|    | 6.4.  | Characterization Tests                                                      | 64 |

| 7. | LEG/  | AL INFORMATION                                                              | 65 |

|    | 7.1.  | Japan Radio and Telecom Approval                                            | 65 |

|    | 7.2.  | Korean Approval                                                             |    |

|    | 7.3.  | FCC Statement                                                               | 65 |

|    | 7.3   | 3.1. Radiation Exposure Statement                                           | 66 |

|    | 7.3   | 3.2. End Product Labeling                                                   |    |

|    |       | 3.3. Manual Information to the End User                                     |    |

|    |       | 3.4. Antenna Installation                                                   |    |

|    | 7.4.  | IC Statement                                                                | 67 |

|    |       | 4.1. Radiation Exposure Statement / Déclaration d'Exposition aux Radiations |    |

|    |          | ND ABBREVIATIONS                                                                |      |

|----|----------|---------------------------------------------------------------------------------|------|

| 8. | ORDFRING | G INFORMATION                                                                   | . 70 |

|    | 7.4.3.   | Manual Information to the End User / Manuel d'Information à l'Utilisateur Final | 69   |

|    | 7.4.2.   | End Product Labeling / Plaque Signalétique du Produit Final                     | 69   |

# List of Figures

| Figure 1.  | Architecture Overview                                     | 16 |

|------------|-----------------------------------------------------------|----|

| Figure 2.  | Mechanical Overview (Top View)                            | 17 |

| Figure 3.  | Pad Configuration (Top View through Module)               | 26 |

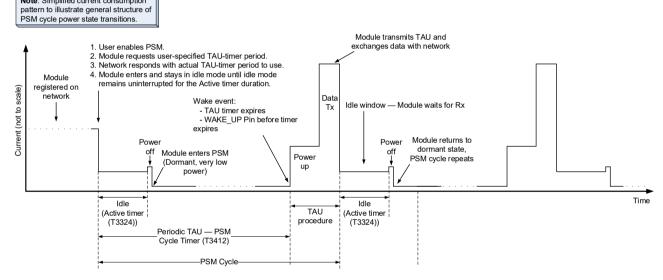

| Figure 4.  | PSM Example (Simplified)                                  | 32 |

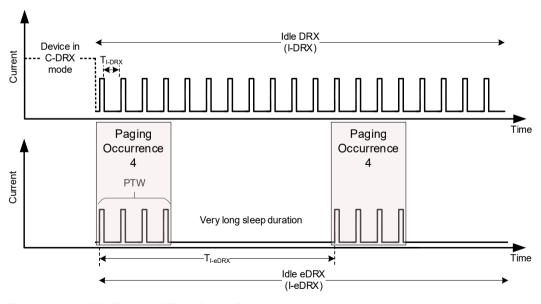

| Figure 5.  | eDRX Example (PTW: 4 Paging Occurrences)                  | 33 |

| Figure 6.  | eDRX Power Consumption Profile Interruption               | 34 |

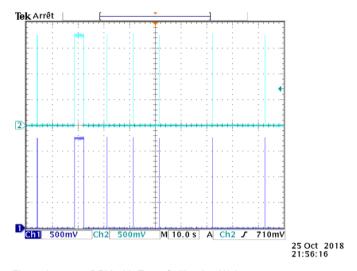

| Figure 7.  | PSM I/O Toggling during TAU and the Active Window (T3324) | 37 |

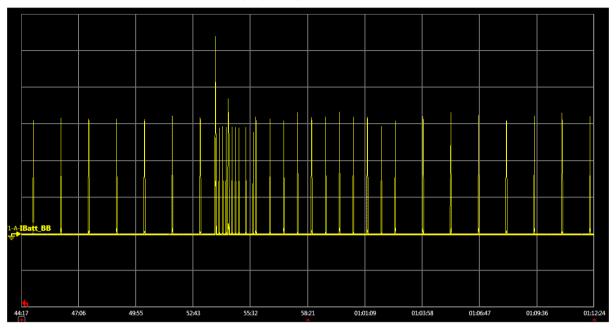

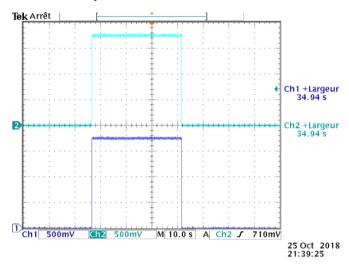

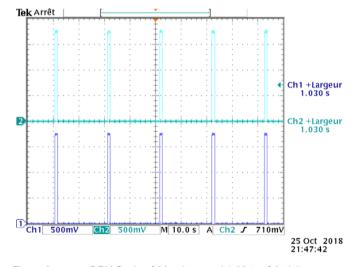

| Figure 8.  | eDRX Cycle of 20s sleep and 1.024s of Activity            | 37 |

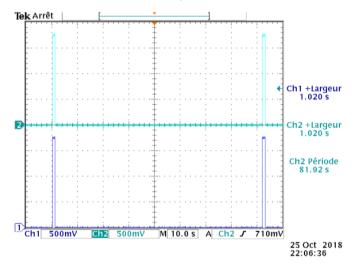

| Figure 9.  | eDRX with Extra Calibration Wakes                         | 38 |

| Figure 10. | Stable eDRX Cycle of 81.92s after Calibration             | 38 |

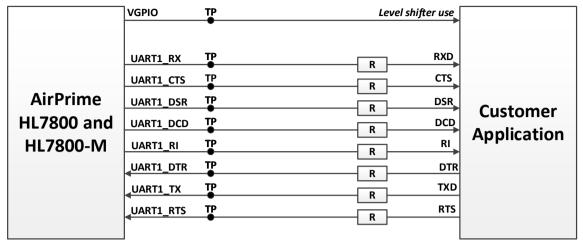

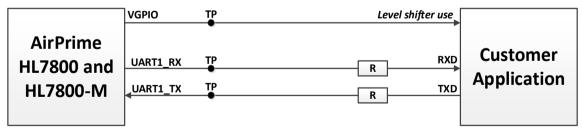

| Figure 11. | 8-wire UART Application Example                           | 44 |

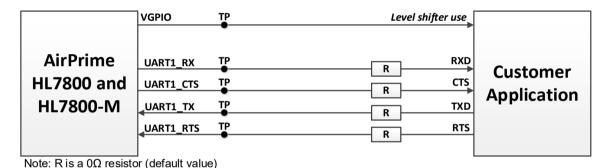

| Figure 12. | 4-wire UART Application Example                           | 44 |

| Figure 13. | 2-wire UART Application Example                           | 44 |

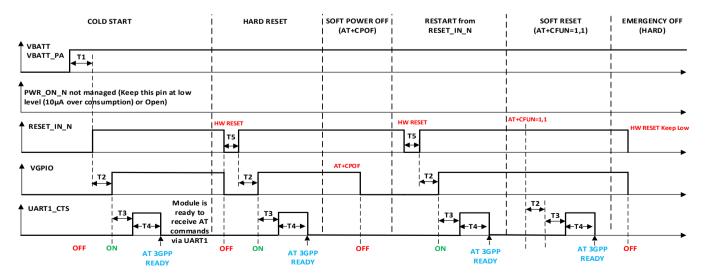

| Figure 14. | Power Up and Power Down Sequence without PWR_ON_N         | 45 |

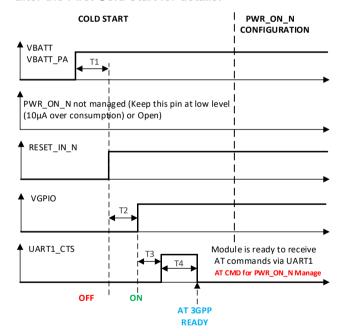

| Figure 15. | Power Up Sequence with PWR_ON_N Cold Start                | 46 |

| Figure 16. | Power On Sequence with PWR_ON_N                           | 47 |

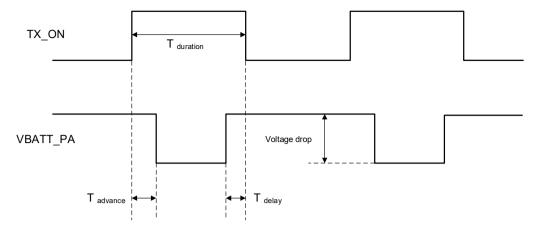

| Figure 17. | TX_ON State during TX Burst                               | 54 |

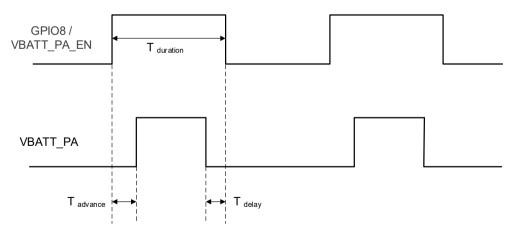

| Figure 18. | VBATT_PA_EN State during RX/TX windows                    | 54 |

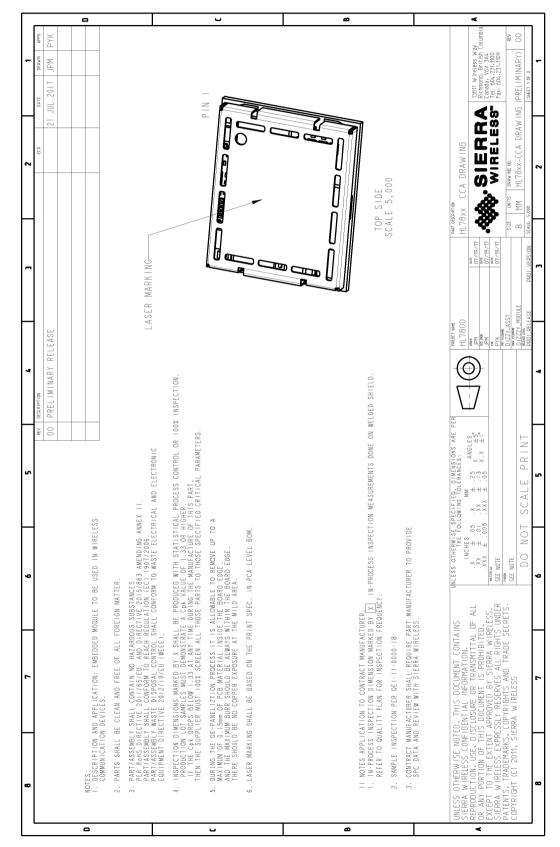

| Figure 19. | Mechanical Drawing                                        | 56 |

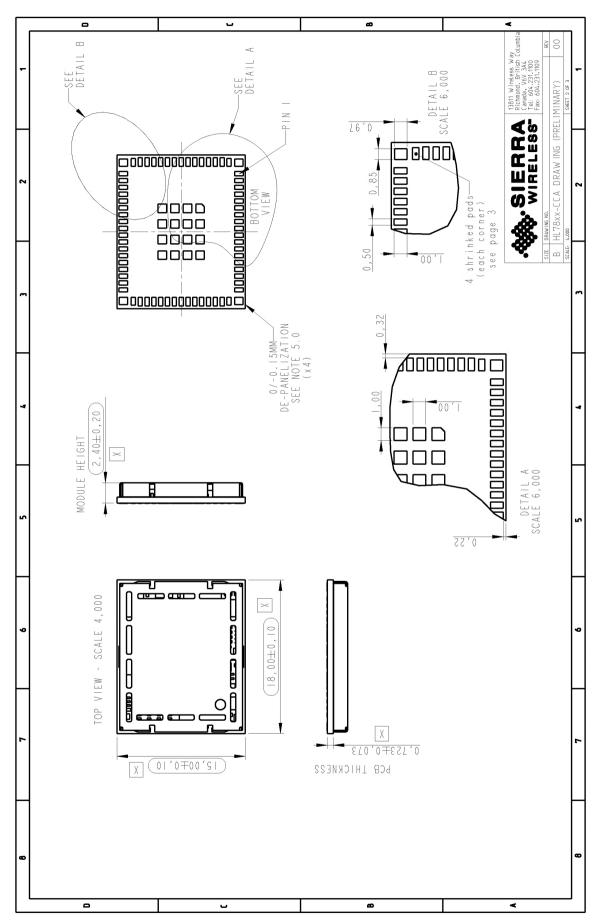

| Figure 20. | Dimensions Drawing                                        | 57 |

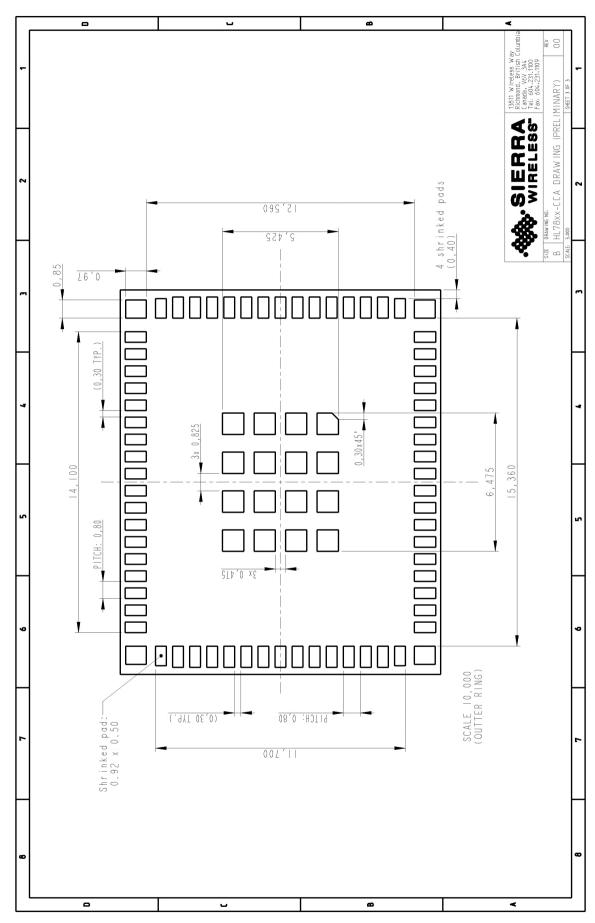

| Figure 21. | Footprint Drawing                                         | 58 |

| Figure 22. | EMC and ESD Components Close to the USIM                  | 60 |

| Figure 23. | ESD Protection for USB                                    | 60 |

| Figure 24. | Antenna Connection                                        | 61 |

| Figure 25. | Sample Japan Certification Indication                     | 65 |

| Figure 26. | Sample Korean Approval                                    | 65 |

41111094 Rev 7 October 04, 2019 10

# List of Tables

| Table 1.  | Supported Bands/Connectivity                                                   | 13 |

|-----------|--------------------------------------------------------------------------------|----|

| Table 2.  | General Features                                                               | 14 |

| Table 3.  | Environmental Specifications                                                   | 18 |

| Table 4.  | Values for ATEX Compliance                                                     | 19 |

| Table 5.  | Pin Definition                                                                 | 21 |

| Table 6.  | Pin Type Codes                                                                 | 25 |

| Table 7.  | Power Supply Pin Description                                                   | 27 |

| Table 8.  | Power Supply Electrical Characteristics                                        | 27 |

| Table 9.  | Maximum Current Consumption                                                    | 27 |

| Table 10. | Low Current Consumption Mode Cat-M1                                            | 28 |

| Table 11. | Low Current Consumption Mode Cat-NB1                                           | 29 |

| Table 12. | Typical Current Consumption for LTE Cat-M1 in Connected Mode for All Bands     | 30 |

| Table 13. | Expected Typical Current Consumption for NB -1 in Connected Mode for All Bands | 30 |

| Table 14. | eDRX-Related Commands                                                          | 34 |

| Table 15. | Low Power Modes                                                                | 35 |

| Table 16. | VGPIO Pin Description                                                          | 39 |

| Table 17. | VGPIO Electrical Characteristics                                               | 39 |

| Table 18. | BAT_RTC Electrical Characteristics                                             | 39 |

| Table 19. | USIM1 Pin Description                                                          | 40 |

| Table 20. | USIM1 Electrical Characteristics                                               | 40 |

| Table 21. | USB Pin Description                                                            | 41 |

| Table 22. | USB Electrical Characteristics                                                 | 41 |

| Table 23. | Digital I/O Electrical Characteristics                                         | 42 |

| Table 24. | GPIO Pin Description                                                           | 42 |

| Table 25. | UART1 Pin Description                                                          | 43 |

| Table 26. | PWR_ON_N Pin Description                                                       | 45 |

| Table 27. | PWR_ON_N Electrical Characteristics                                            | 45 |

| Table 28. | PWR_ON_N Not Managed Timing                                                    | 46 |

| Table 29. | PWR_ON_N Managed Timing                                                        | 47 |

| Table 30. | RESET_IN_N Pin Description                                                     | 48 |

| Table 31. | RESET_IN_N Electrical Characteristics                                          | 48 |

| Table 32. | ADC Pin Description                                                            | 48 |

| Table 33. | ADC Electrical Characteristics                                                 | 48 |

| Table 34. | Clock Interface Pin Description                                                | 49 |

| Table 35. | CLI Interface Pin Description.                                                 | 49 |

| Table 36. | Modem Logs Interface Pin Description                                           | 50 |

| Table 37. | WAKE_UP Pin Description                                                        | 50 |

|           |                                                                                |    |

#### **Product Technical Specification**

| Table 38. | WAKE_UP Electrical Characteristics50         |

|-----------|----------------------------------------------|

| Table 39. | FAST_SHUTDOWN_N Pin Description51            |

| Table 40. | FAST_SHUTDOWN_N Electrical Characteristics51 |

| Table 41. | RF Main Pin Description51                    |

| Table 42. | Maximum Output Power52                       |

| Table 43. | Typical Conducted Cat-M1 RX Sensitivity      |

| Table 44. | Typical Conducted NB1 RX Sensitivity53       |

| Table 45. | TX_ON Pin Description53                      |

| Table 46. | VBATT_PA_EN Pin Description54                |

| Table 47. | VBATT_PA_EN Characteristics                  |

| Table 48. | GPS Antenna Specifications                   |

| Table 49. | GPS Performance                              |

| Table 50. | Preconditioning Test62                       |

| Table 51. | Performance Test 62                          |

| Table 52. | Aging Tests63                                |

| Table 53. | Characterization Tests64                     |

| Table 54. | Ordering Information70                       |

## 1. Introduction

This document is the Product Technical Specification for the AirPrime HL7800 and HL7800-M Embedded Modules designed for M2M and Internet of Things (IoT) markets. It defines the high-level product features and illustrates the interfaces for these features. This document is intended to cover the hardware aspects of the product, including electrical and mechanical.

The AirPrime HL7800 and HL7800-M modules belong to the AirPrime HL Series from the Essential Connectivity Module family. These are industrial grade Embedded Wireless Modules that provides data connectivity on LTE (as listed in Table 1 Supported Bands/Connectivity).

The AirPrime HL7800 and HL7800-M modules support a large variety of interfaces such as USB FS, UART, ADC, GPIOs, and also support the new ultra-low-power-consumption hibernation modes to provide customers with the highest level of flexibility in implementing high-end solutions.

Table 1. Supported Bands/Connectivity

| LTE<br>Band | Transmit Band (Tx) |            | Receive Band (Rx) |            | Cat-M1<br>(HL7800 and | Cat-NB1<br>(HL7800 |

|-------------|--------------------|------------|-------------------|------------|-----------------------|--------------------|

| Zuna        | Minimum            | Maximum    | Minimum           | Maximum    | HL7800-M)             | only)              |

| B1          | 1920 MHz           | 1980 MHz   | 2110 MHz          | 2170 MHz   | ✓                     | ✓                  |

| B2          | 1850 MHz           | 1910 MHz   | 1930 MHz          | 1990 MHz   | ✓                     | ✓                  |

| В3          | 1710 MHz           | 1785 MHz   | 1805 MHz          | 1880 MHz   | ✓                     | ✓                  |

| B4          | 1710 MHz           | 1755 MHz   | 2110 MHz          | 2155 MHz   | ✓                     | ✓                  |

| B5          | 824 MHz            | 849 MHz    | 869 MHz           | 894 MHz    | ✓                     | ✓                  |

| B8          | 880 MHz            | 915 MHz    | 925 MHz           | 960 MHz    | ✓                     | ✓                  |

| В9          | 1749.9 MHz         | 1784.9 MHz | 1844.9 MHz        | 1879.9 MHz | *                     | *                  |

| B10         | 1710 MHz           | 1770 MHz   | 2110 MHz          | 2170 MHz   | *                     | *                  |

| B12         | 699 MHz            | 716 MHz    | 729 MHz           | 746 MHz    | ✓                     | ✓                  |

| B13         | 777 MHz            | 787 MHz    | 746 MHz           | 756 MHz    | ✓                     | ✓                  |

| B14         | 788 MHz            | 798 MHz    | 758 MHz           | 768 MHz    | ✓                     | ✓                  |

| B17         | 704 MHz            | 716 MHz    | 734 MHz           | 746 MHz    | *                     | ✓                  |

| B18         | 815 MHz            | 830 MHz    | 860 MHz           | 875 MHz    | ✓                     | ✓                  |

| B19         | 830 MHz            | 845 MHz    | 875 MHz           | 890 MHz    | ✓                     | ✓                  |

| B20         | 832 MHz            | 862 MHz    | 791 MHz           | 821 MHz    | ✓                     | ✓                  |

| B25         | 1850 MHz           | 1915 MHz   | 1930 MHz          | 1995 MHz   | ✓                     | ✓                  |

| B26         | 814 MHz            | 849 MHz    | 859 MHz           | 894 MHz    | ✓                     | ✓                  |

| B27         | 807 MHz            | 824 MHz    | 852 MHz           | 869 MHz    | ✓                     | *                  |

| B28         | 703 MHz            | 748 MHz    | 758 MHz           | 803 MHz    | ✓                     | ✓                  |

| B66         | 1710 MHz           | 1780 MHz   | 2110 MHz          | 2200 MHz   | ✓                     | ✓                  |

<sup>\*</sup> Will be supported in a future release.

Note: RF bands supported are configurable through AT command. The software-based radio allows for the ability to support extra bands for worldwide connectivity.

## 1.1. Common Flexible Form Factor (CF<sup>3</sup>)

The AirPrime HL7800 and HL7800-M modules belong to the Common Flexible Form Factor (CF³) family of modules. This family consists of a series of WWAN modules that share the same mechanical dimensions (same width and length with varying thicknesses) and footprint. The CF³ form factor provides a unique solution to a series of problems faced commonly in the WWAN module space as it:

- Accommodates multiple radio technologies (LTE advanced) and band groupings.

- Supports bit-pipe (Essential Module Series) and value add (Smart Module Series) solutions.

- Offers electrical and functional compatibility.

- Provides Direct Mount as well as Socket-ability depending on customer needs.

## 1.2. Physical Dimensions

AirPrime HL7800 and HL7800-M modules are compact, robust, fully shielded modules with the following dimensions:

Length: 18.0 mmWidth: 15.0 mmThickness: 2.4 mmWeight: 1.17 g

Note: Dimensions specified above are typical values.

#### 1.3. General Features

The table below summarizes the AirPrime HL7800 and HL7800-M's features.

Table 2. General Features

| Feature      | Description                                                                       |  |  |

|--------------|-----------------------------------------------------------------------------------|--|--|

|              | Small form factor (86-pad solderable LGA pad) – 15.0mm x 18.0mm x 2.4mm (nominal) |  |  |

| Physical     | Metal shield can                                                                  |  |  |

|              | RF connection pads (RF main and RF GPS)                                           |  |  |

|              | Baseband signals connection                                                       |  |  |

| Power supply | Single or double supply voltage (VBATT and VBATT_PA) – 3.2V – 4.35V               |  |  |

| Feature               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF                    | <ul> <li>Cat-M1         <ul> <li>Power Class 3 (23dBm)</li> <li>Software based radio allowing support of extra bands for worldwide operation (will be supported in a future release)</li> </ul> </li> <li>Cat-NB1 (not supported on the HL7800-M)         <ul> <li>Power Class 3 (23dBm)</li> <li>Software based radio allowing support of extra bands for worldwide operation (will be supported in a future release)</li> </ul> </li> <li>GPS*         <ul> <li>1575.42 MHz</li> </ul> </li> <li>Note: The GPS receiver shares the same RF resources as the 4G receiver. The end-device target should allow GPS positioning for asset management applications where infrequent and no real-time position updates are required.</li> </ul>                       |

| SIM interface         | <ul> <li>1.8V only support (legacy 3V SIM is not supported; this should not have any impact on design)         (Note: Modern SIM cards all support 1.8V.)</li> <li>SIM extraction / hot plug detection</li> <li>SIM/USIM support</li> <li>Conforms with ETSI UICC Specifications.</li> <li>Supports SIM application tool kit with proactive SIM commands</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| Application interface | <ul> <li>AT command interface – 3GPP 27.007 standard, plus proprietary extended AT commands</li> <li>CMUX multiplexing over UART</li> <li>USB Full Speed (FS)*</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Protocol stack        | Cat-M1  3GPP Rel. 13  Half-duplex  Channel bandwidth 1.4MHz  LTE carrier bandwidth 1.4 / 3 / 5 / 10 / 15 / 20 MHz  Up to 375kbit/s uplink, 300 kbit/s downlink  Extended Coverage Mode A  PSM (Power Save Mode)  I-DRX (Idle Mode Discontinuous Reception)  C-DRX (Connected Mode Discontinuous Reception)  Idle mode mobility  Connected mode mobility  connected mode mobility  connected mode HL7800-M)  GiOT optimizations (U-Plane, C-Plan)*  Cat-NB1 (not supported on the HL7800-M)  3GPP Rel. 13  Half-duplex  Channel bandwidth 180KHz  LTE carrier bandwidth 1.4 / 3 / 5 / 10 / 15 / 20 MHz  Up to 100 kbit/s in downlink  Operational mode — Inband, Guard band, Standalone  CioT EPS optimizations (Data over NAS)  NIDD over SGEF  Extended coverage |

| Feature        | Description                                                                                                                                                                  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol stack | <ul> <li>Flexible selection</li> <li>Manual system selection across RATs</li> </ul>                                                                                          |

|                | <ul> <li>Dynamic system selection across RATs (preferred RAT)*</li> </ul>                                                                                                    |

|                | SMS over SG                                                                                                                                                                  |

| SMS            | MO/MT                                                                                                                                                                        |

|                | SMS storage to SIM card or ME storage                                                                                                                                        |

|                | Multiple cellular packet data profiles                                                                                                                                       |

|                | Sleep mode for minimum idle power draw                                                                                                                                       |

|                | Mobile-originated PDP context activation / deactivation                                                                                                                      |

| Connectivity   | <ul> <li>Static and Dynamic IP address. The network may assign a fixed IP address or<br/>dynamically assign one using DHCP (Dynamic Host Configuration Protocol).</li> </ul> |

|                | <ul> <li>PDP context type (IPv4, IPv6, IPv4v6). IP Packet Data Protocol context</li> </ul>                                                                                   |

|                | RFC1144 TCP/IP header compression                                                                                                                                            |

|                | Operating temperature ranges (industrial grade):                                                                                                                             |

| Environmental  | Class A: -30°C to +70°C                                                                                                                                                      |

|                | Class B: -40°C to +85°C                                                                                                                                                      |

| RTC            | Real Time Clock (RTC)*                                                                                                                                                       |

<sup>\*</sup> Will be available in a future release.

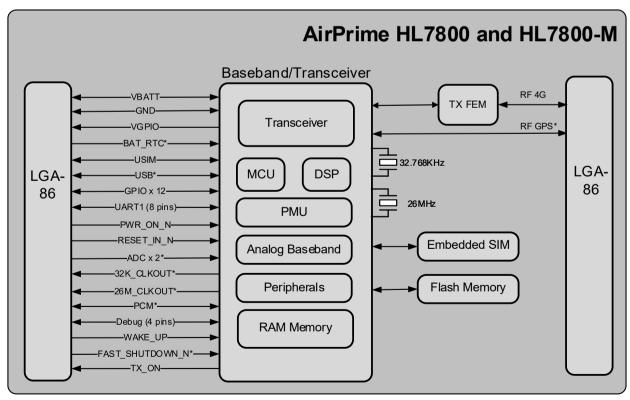

#### 1.4. Architecture

The figure below presents an overview of the AirPrime HL7800 and HL7800-M's internal architecture and external interfaces.

\* Will be available in a future release

Figure 1. Architecture Overview

#### 1.5. Interfaces

The AirPrime HL7800 and HL7800-M modules provide the following interfaces and peripheral connectivity:

- 1x VGPIO (1.8V)

- 1x BAT RTC backup battery interface (will be available in a future firmware release)

- 1x 1.8V USIM

- 1x USB FS

- 12x GPIOs

- 1x 8-wire UART

- 1x Active Low POWER ON (will be available in a future firmware release)

- 1x Active Low RESET

- 2x ADC

- 2x System clock out (32.768 KHz and 26 MHz)

- 1x PCM (will be available in a future firmware release)

- 1x 4-wire UART for debug interface only

- 1x Wake up signal

- 1x Fast shutdown signal (will be available in a future firmware release)

- 1x Main RF Antenna

- 1x TX indicator

- 1x GPS Antenna (will be available in a future firmware release)

#### 1.6. Connection Interface

AirPrime HL7800 and HL7800-M modules are LGA form factor devices. All electrical and mechanical connections are made through the 86 Land Grid Array (LGA) pads on the bottom side of the PCB.

Figure 2. Mechanical Overview (Top View)

The 86 pads have the following distribution:

- 66 inner signal pads, 1x0.5mm, pitch 0.8mm

- 16 inner ground pads, 1.0x1.0mm, pitch 1.825mm/1.475mm

- 4 outer corner ground pads, 0.85x0.97mm

## 1.7. ESD Specifications

• IEC-61000-4-2 (test carried out on test vehicle including ESD protection)

Contact Voltage: ±2kV, ±4kV, ±6kV

GPS pad C38: ±500V

Air Voltage: ±2kV, ±4kV, ±8kV

JESD22-A114 ± 250V Human Body Model

• JESD22-C101C ± 250V Charged Device Model

#### 1.8. Environmental and Certifications

#### 1.8.1. Environmental Specifications

The environmental specification for both operating and storage conditions are defined in the table below.

Table 3. Environmental Specifications

| Conditions        | Range          |

|-------------------|----------------|

| Operating Class A | -30°C to +70°C |

| Operating Class B | -40°C to +85°C |

| Storage           | -40°C to +85°C |

Class A is defined as the operating temperature ranges that the device:

- Shall exhibit normal function during and after environmental exposure.

- Shall meet the minimum requirements of 3GPP or appropriate wireless standards.

Class B is defined as the operating temperature ranges that the device:

- Shall remain fully functional during and after environmental exposure

- Shall exhibit the ability to establish an SMS or DATA call (emergency call) at all times even

when one or more environmental constraint exceeds the specified tolerance.

- Unless otherwise stated, full performance should return to normal after the excessive constraint(s) have been removed.

#### 1.8.2. Frequency Drift Correction

The HL7800 and HL7800-M are environment-sensitive like any electronic device, but able to correct temperature and aging effects automatically. Parameters to be considered when addressing the environmental effect on the HL7800 and HL7800-M are as follows:

Maximum deviation correction: 20 ppm

Environmental Temperature effect: 0.5 ppm

Factory reflow effect: 1 ppm + 1 ppm / reflow

Aging effect: 1 ppm /year of use

For example, if an HL7800 module is mounted on a single side (1 reflow) customer PCB and used for 10 years between -40 and +85 $^{\circ}$ C, the frequency drift will be up to 0.5 + (1 + 1) + (1 \* 10) = 12.5 ppm, which is in the limits of the 20 ppm maximum correction.

#### 1.8.3. ATEX Compliance

The following table lists the inductor and capacitor values to be considered for ATEX certification of the system hosting the HL7800 and HL7800-M modules. All supplies in the modules are linear LDO except for one 1.3V DC/DC step-down.

Table 4. Values for ATEX Compliance

| Parameter         | Value    | Tolerance |

|-------------------|----------|-----------|

| Total Inductance  | 2.21 μH  | 30%       |

| Total Capacitance | 43.64 µF | 20%       |

#### 1.8.4. Regulatory

The AirPrime HL7800 and HL7800-M modules will be compliant with the following regulations:

- RED

- FCC

- IC

- RCM

- JRF/JPA

- KC

## 1.8.5. RoHS Directive Compliance

AirPrime HL7800 and HL7800-M modules are compliant with RoHS Directive 2011/65/EU, including directive 2015/863 amending annex II, which sets limits for the use of certain restricted hazardous substances. This directive states that electrical and electronic equipment put on the market does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB), polybrominated diphenyl ethers (PBDE), Bis (2-ethylhexyl) phthalate (DEHP), Butyl benzyl phthalate (BBP), Dibutyl phthalate (DBP) or Di-isobutyl phthalate (DIBP) above threshold limits.

#### 1.8.6. Disposing of the Product

This electronic product is subject to the EU Directive 2012/19/EU for Waste Electrical and Electronic Equipment (WEEE). As such, this product must not be disposed of at a municipal waste collection point. Please refer to local regulations for directions on how to dispose of this product in an environmentally friendly manner.

## 1.9. References

[1] AirPrime HL78xx Customer Process Guidelines

Reference Number: 41112095

[2] AirPrime HL78xx AT Commands Interface Guide

Reference Number: 41111821

[3] AirPrime HL Series Development Kit User Guide

Reference Number: 4114877

[4] AirPrime HL7800 Low Power Modes Application Note

Reference Number: 2174229

[5] AirPrime HL7800-M MNO and RF Band Customization at Customer Production Site

**Application Note**

Reference Number: 2174213

## 2. Pad Definition

AirPrime HL7800 and HL7800-M pins are divided into 2 functional categories.

- Core functions and associated pins cover all the mandatory features for M2M connectivity and will be available by default across all CF<sup>3</sup> family of modules. These Core functions are always available and always at the same physical pad locations. A customer platform using only these functions and associated pads are guaranteed to be forward and/or backward compatible with the next generation of CF<sup>3</sup> modules.

- Extension functions and associated pins bring additional capabilities to the customer. Whenever an Extension function is available on a module, it is always at the same pad location.

Other pins marked as "not connected" or "reserved" should not be used.

Table 5. Pin Definition

| Pad # | Signal Name | Function                       | I/O | Pre and Post<br>Reset State* | Power Supply<br>Domain | Recommendation for Unused Pads | Туре      |

|-------|-------------|--------------------------------|-----|------------------------------|------------------------|--------------------------------|-----------|

| C1    | GPIO1       | General purpose input/output   | I/O | PU                           | 1.8V (VGPIO)           | Left open                      | Extension |

| C2    | UART1_RI    | UART1 Ring indicator           | 0   | PU**                         | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C3    | UART1_RTS   | UART1 Request to send          | I   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C4    | UART1_CTS   | UART1 Clear to send            | 0   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C5    | UART1_TX    | UART1 Transmit data            | I   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C6    | UART1_RX    | UART1 Receive data             | 0   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C7    | UART1_DTR   | UART1 Data terminal ready      | I   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C8    | UART1_DCD   | UART1 Data carrier detect      | 0   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C9    | UART1_DSR   | UART1 Data set ready           | 0   | PU                           | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C10   | GPIO2       | General purpose input/output   | I/O | PD**                         | 1.8V (VGPIO)           | Connect to test point          | Core      |

| C11   | RESET_IN_N  | Input reset signal             | 1   | PU                           | 1.8V                   | Left open                      | Core      |

| C12   | USB_D-      | USB Data Negative (Full Speed) | I/O |                              | 3.3V                   | Connect to test point          | Extension |

| C13   | USB_D+      | USB Data Positive (Full Speed) | I/O |                              | 3.3V                   | Connect to test point          | Extension |

| Pad # | Signal Name | Function                      | I/O | Pre and Post<br>Reset State* | Power Supply<br>Domain | Recommendation for Unused Pads              | Туре          |

|-------|-------------|-------------------------------|-----|------------------------------|------------------------|---------------------------------------------|---------------|

| C14   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not connected |

| C15   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not connected |

| C16   | USB_VBUS    | USB VBUS                      | I   |                              | 5V                     | Mandatory connection if USB is used         | Extension     |

| C17   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not connected |

| C18   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not connected |

| C19   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not Connected |

| C20   | NC          | Not Connected                 |     |                              |                        | Left open                                   | Not Connected |

| C21   | BAT_RTC     | Power supply for RTC backup   | I   |                              |                        | Left open                                   | Extension     |

| C22   | 26M_CLKOUT  | 26M System Clock Output       | 0   | PD                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C23   | 32K_CLKOUT  | 32.768kHz System Clock Output | 0   | PU                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C24   | ADC1        | Analog to digital converter   | I   | PD                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C25   | ADC0        | Analog to digital converter   | 1   | PU                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C26   | UIM1_VCC    | 1.8V USIM1 Power supply       | 0   |                              | 1.8V                   | Mandatory connection                        | Core          |

| C27   | UIM1_CLK    | 1.8V USIM1 Clock              | 0   | PD                           | 1.8V (VGPIO)           | Mandatory connection                        | Core          |

| C28   | UIM1_DATA   | 1.8V USIM1 Data               | I/O | PD                           | 1.8V (VGPIO)           | Mandatory connection                        | Core          |

| C29   | UIM1_RESET  | 1.8V USIM1 Reset              | 0   | PD                           | 1.8V (VGPIO)           | Mandatory connection                        | Core          |

| C30   | GND         | Ground                        | 0V  |                              | 0V                     | Recommended connection but can be left open | Extension     |

| C31   | NC          | Not Connected                 |     |                              |                        |                                             | Not connected |

| C32   | GND         | Ground                        | 0V  |                              | 0V                     | Recommended connection but can be left open | Extension     |

| C33   | PCM_OUT     | PCM data out                  | 0   | PU                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C34   | PCM_IN      | PCM data in                   | I   | PU                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C35   | PCM_SYNC    | PCM sync out                  | I/O | PU                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| C36   | PCM_CLK     | PCM clock                     | I/O | PD                           | 1.8V (VGPIO)           | Left open                                   | Extension     |

| Pad # | Signal Name         | Function                                                   | I/O | Pre and Post<br>Reset State* | Power Supply<br>Domain | Recommendation for Unused Pads | Туре          |

|-------|---------------------|------------------------------------------------------------|-----|------------------------------|------------------------|--------------------------------|---------------|

| C37   | GND                 | Ground                                                     | 0V  |                              | 0V                     | Mandatory connection           | Core          |

| C38   | RF_GPS              | RF_GPS                                                     |     |                              |                        | Left open                      | Core          |

| C39   | GND                 | Ground                                                     | 0V  |                              | 0V                     | Mandatory connection           | Core          |

| C40   | GPIO7               | General purpose input/output                               | I/O | PU                           | 1.8V (VGPIO)           | Left open                      | Core          |

| C41   | GPIO8 / VBATT_PA_EN | General purpose input/output / External RF voltage control | I/O | PD                           | 1.8V (VGPIO)           | Left open                      | Core          |

| C42   | NC                  | Not Connected                                              |     |                              |                        |                                | Not connected |

| C43   | EXT_LNA_GPS_EN      | External GPS LNA enable                                    |     | PU                           |                        | Left open                      | Extension     |

| C44   | WAKE_UP             | Wake up signal                                             | 1   |                              | 1.8V                   | Mandatory connection           | Extension     |

| C45   | VGPIO               | GPIO voltage output                                        | 0   |                              | 1.8V (VGPIO)           | Left open                      | Core          |

| C46   | GPIO6               | General purpose input/output                               | I/O | PD                           | 1.8V (VGPIO)           | Left open                      | Core          |

| C47   | NC                  | Not Connected                                              |     |                              |                        | Left open                      | Not connected |

| C48   | GND                 | Ground                                                     | 0V  |                              | 0V                     | Mandatory connection           | Core          |

| C49   | RF_MAIN             | RF Input/output                                            |     |                              |                        | Mandatory connection           | Core          |

| C50   | GND                 | Ground                                                     | 0V  |                              | 0V                     | Mandatory connection           | Core          |

| C51   | GPIO14              | General purpose input/output                               | I/O | PU                           | 1.8V (VGPIO)           | Connect to test point          | Extension     |

| C52   | GPIO10              | General purpose input/output                               | I/O | PU                           | 1.8V (VGPIO)           | Connect to test point          | Extension     |

| C53   | GPIO11              | General purpose input/output                               | I/O | PU                           | 1.8V (VGPIO)           | Connect to test point          | Extension     |

| C54   | GPIO15              | General purpose input/output                               | I/O | PU                           | 1.8V (VGPIO)           | Connect to test point          | Extension     |

| C55   | UART0_RX            | Debug Receive data                                         | 0   | PU                           | 1.8V (VGPIO)           | Mandatory connection           | Extension     |

| C56   | UART0_TX            | Debug Transmit data                                        | 1   | PU                           | 1.8V (VGPIO)           | Mandatory connection           | Extension     |

| C57   | UARTO_CTS           | Debug Clear to Send                                        | 0   | PU                           | 1.8V (VGPIO)           | Mandatory connection           | Extension     |

| C58   | UART0_RTS           | Debug Request to Send                                      | 1   | PD                           | 1.8V (VGPIO)           | Mandatory connection           | Extension     |

| C59   | PWR_ON_N            | Active Low Power On control signal                         | I   |                              | 1.8V                   | Mandatory connection           | Core          |

| C60   | TX_ON               | TX transmission indication                                 | 0   | PU                           | 1.8V (VGPIO)           | Left open                      | Extension     |

| Pad #                  | Signal Name                | Function                                                              | I/O | Pre and Post<br>Reset State* | Power Supply<br>Domain                  | Recommendation for Unused Pads | Туре      |

|------------------------|----------------------------|-----------------------------------------------------------------------|-----|------------------------------|-----------------------------------------|--------------------------------|-----------|

| C61                    | VBATT_PA                   | Power supply (refer to section 3.1 Power Supply for more information) | 1   |                              | 3.2V (min)<br>3.7V (typ)<br>4.35V (max) | Mandatory connection           | Core      |

| C62                    | VBATT_PA                   | Power supply (refer to section 3.1 Power Supply for more information) | 1   |                              | 3.2V (min)<br>3.7V (typ)<br>4.35V (max) | Mandatory connection           | Core      |

| C63                    | VBATT                      | Power supply (refer to section 3.1 Power Supply for more information) | I   |                              | 3.2V (min)<br>3.7V (typ)<br>4.35V (max) | Mandatory connection           | Core      |

| C64                    | UIM1_DET / GPIO3           | USIM1 Detection / General purpose input/output                        | I/O | PD                           | 1.8V (VGPIO)                            | Left open                      | Core      |

| C65                    | FAST_SHUTDOWN_N /<br>GPIO4 | Fast Shutdown signal / General purpose input/output                   | I/O | PU                           | 1.8V (VGPIO)                            | Left open                      | Extension |

| C66                    | GPIO5                      | General purpose input/output                                          | I/O | PU                           | 1.8V (VGPIO)                            | Left open                      | Extension |

| CG1 – CG4,<br>G1 – G16 | GND                        | Ground                                                                | GND |                              | 0V                                      |                                | Core      |

<sup>\*</sup> This refers to the state before and after RESET\_IN\_N; state is Undefined during Reset, Hibernate or OFF modes. Refer to section 3.12 Reset Signal (RESET\_IN\_N) for more details.

<sup>\*\*</sup> During hibernation (not applicable to Lite Hibernate mode), all the pulled up (PU) signals will toggle at the rate of wake events. Therefore, if the RI signal is to be used in a system to warn the main MCU of an incoming network event (like SMS or DATA), this RI signal cannot be used as it will toggle at the rate of the eDRX or PSM recurrent wakes. It is therefore recommended to use GPIO2 with a built-in pull down (PD) instead of RI. This will allow the module to trigger the GPIO instead of the RI safely, without unwanted toggles.

Product Technical Specification Pad Definition

# 2.1. Pin Types

Table 6. Pin Type Codes

| Туре | Definition                      |  |

|------|---------------------------------|--|

| 1    | Digital Input                   |  |

| 0    | Digital Output                  |  |

| I/O  | Digital Input / Output          |  |

| Т    | Tristate                        |  |

| T/PU | Tristate with pull-up enabled   |  |

| T/PD | Tristate with pull-down enabled |  |

| PU   | Pull-up enabled                 |  |

| PD   | Pull-down enabled               |  |

| N/A  | Not Applicable                  |  |

Product Technical Specification Pad Definition

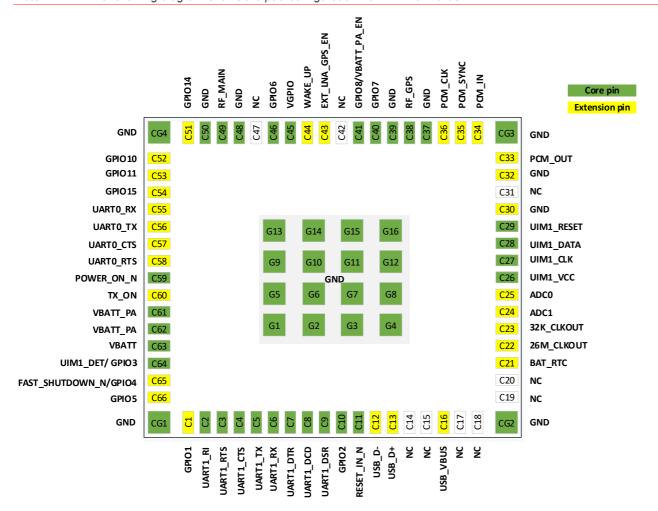

## 2.2. Pad Configuration (Top View, Through Module)

Note: The following diagram shows the pad configuration from DV2 onwards.

Figure 3. Pad Configuration (Top View through Module)

## 3. Detailed Interface Specifications

Note:

If not specified, all electrical values are given for VBATT=3.7V and an operating temperature of 25°C.

For standard applications, VBATT and VBATT\_PA must be tied externally to the same power supply. For some specific applications, the module supports separate VBATT and VBATT\_PA connection if the requirements below are fulfilled.

## 3.1. Power Supply

The AirPrime HL7800 and HL7800-M modules are supplied through the VBATT and VBATT\_PA signals.

Note:

The rise of the VBATT power signal initiates the power on sequence of the module. Refer to sections 3.11 Power On Signal (PWR\_ON\_N) and 3.12 Reset Signal (RESET\_IN\_N) for additional information.

Refer to the following table for the pin description of the Power Supply interface.

Table 7. Power Supply Pin Description

| Pad Number          | Signal Name | I/O | Description                    |

|---------------------|-------------|-----|--------------------------------|

| C63                 | VBATT       | 1   | Power supply (base band)       |

| C61, C62            | VBATT_PA    | 1   | Power supply (radio frequency) |

| CG1 – CG4, G1 – G16 | GND         |     | Ground                         |

Refer to the following table for the electrical characteristics of the Power Supply interface.

Table 8. Power Supply Electrical Characteristics

| Supply                                  | Minimum | Typical | Maximum |

|-----------------------------------------|---------|---------|---------|

| VBATT voltage (V)                       | 3.2     | 3.7     | 4.35    |

| VBATT_PA voltage (V) Full Specification | 3.2     | 3.7     | 4.35    |

| VBATT_PA voltage (V) Extended Range     | 2.8*    | 3.7     | 4.35    |

<sup>\*</sup> No guarantee of 3GPP performances for VBATT\_PA from 2.8 to 3.2V.

Table 9. Maximum Current Consumption

| Supply   | Maximum |

|----------|---------|

| VBATT    | 300mA   |

| VBATT_PA | 400mA   |

Note:

If a single PSU is used, the recommended power supply capability is 400 mA + 300 mA = 700 mA.

Maximum values are provided for VSWR 2.5:1 with worst conditions among supported ranges of voltages and temperature (including GPS consumption).

## 3.2. Current Consumption

The following tables list the current consumption of the module at different conditions.

Note:

Typical values are defined for VBATT/VBATT\_PA at 3.7V and 25°C, for  $50\Omega$  impedance at all RF ports. USIM current consumption is not included.

Table 10. Low Current Consumption Mode Cat-M1

| Modem<br>Radio State | Lowest Power<br>Mode              | Configuration                                                    | Typical<br>Average Value              | Unit |

|----------------------|-----------------------------------|------------------------------------------------------------------|---------------------------------------|------|

| OFF                  | OFF                               | Module is switched off by AT command and VBATs are connected     | 1.8                                   | μΑ   |

|                      | Hibernate                         | Floor current                                                    | 1.8                                   | μA   |

|                      | Lite Hibernate                    | Floor current                                                    | 30                                    | μA   |

| DOM                  | Hibernate                         | 1h avala and T2224 = 20a                                         | 175ª                                  | μA   |

| PSM                  | Lite Hibernate                    | 1h cycle and T3324 = 20s                                         | 185ª                                  | μA   |

|                      | Hibernate                         | 24h ayolo and T2224 = 20a                                        | 9 <sup>a</sup>                        | μA   |

|                      | Lite Hibernate                    | - 24h cycle and T3324 = 20s                                      | 35 <sup>a</sup>                       | μA   |

|                      | TAU                               | Occurrence is network dependent                                  | 82                                    | μAh  |

|                      | Calibration                       | Applies to eDRX 81.92s and more                                  | 12                                    | μAh  |

|                      | Hibernate                         | Floor during a DDV                                               | 26                                    | μA   |

|                      | Lite Hibernate <sup>b</sup>       | Floor during eDRX                                                | 28                                    | μΑ   |

|                      | Hibernate Cycle                   | eDRX cycle (TI-eDRX) = 20.48s and                                | 135°                                  | μA   |

| eDRX                 | Lite Hibernate Cycle <sup>b</sup> | PTW and DRX = 1.28s Refer to section 3.3.1.2 Extended DRX (eDRX) | 135°                                  | μΑ   |

|                      | Hibernate Cycle                   | eDRX cycle (TI-eDRX) = 81.92s and                                | 50°                                   | μΑ   |

|                      | Lite Hibernate Cycle <sup>b</sup> | PTW and DRX = 1.28s Refer to section 3.3.1.2 Extended DRX (eDRX) | 55°                                   | μΑ   |

| DRX                  | SMS Reception                     | 50 characters received                                           | 120                                   | μAh  |

|                      | Sleep                             | 1.28s                                                            | 2.4<br>(Target: 450 μA <sup>d</sup> ) | mA   |

|                      | Sieep                             | 2.56s                                                            | 1.9<br>(Target: 300 μA <sup>d</sup> ) | mA   |

|                      | Running                           | DRX independent, <b>+KSLEEP=2</b> or Wake active                 | 35                                    | mA   |

- a Values are T3324 dependent.

- b Recommended mode.

- c Values are PTW and DRX dependent.

- d Enhancement will be available in a future firmware version.

Refer to section 3.3.2 Power Modes for details regarding different low power modes.

The values above assume the following conditions:

- Cat-M1

- Good channel conditions (SINR > 5dB)

- Static scenario

- Cycle includes boot, cell acquisition, network attach, wait for timer expiry and back to sleep

Table 11. Low Current Consumption Mode Cat-NB1

| Modem<br>Radio State | Lowest Power<br>Mode              | Configuration                                                    | Typical<br>Average Value              | Unit |

|----------------------|-----------------------------------|------------------------------------------------------------------|---------------------------------------|------|

| OFF                  | OFF                               | Module is switched off by AT command and VBATs are connected     | 1.8                                   | μΑ   |

|                      | Hibernate                         | Floor current                                                    | 1.8                                   | μA   |

|                      | Lite Hibernate                    | Floor current                                                    | 30                                    | μA   |

| DCM                  | Hibernate                         | 1h avala and T2224 = 20a                                         | 235ª                                  | μA   |

| PSM                  | Lite Hibernate                    | - 1h cycle and T3324 = 20s                                       | 265ª                                  | μA   |

|                      | Hibernate                         | 24h ayolo and T2224 = 20a                                        | 10 <sup>a</sup>                       | μA   |

|                      | Lite Hibernate                    | 24h cycle and T3324 = 20s                                        | 40 <sup>a</sup>                       | μA   |

|                      | TAU                               | Occurrence is network dependent                                  | 100                                   | μAh  |

|                      | Calibration                       | Applies to eDRX 81.92s and more                                  | 21                                    | μAh  |

| eDRX                 | Hibernate                         | El l : DDV                                                       | 22                                    | μA   |

|                      | Lite Hibernate <sup>b</sup>       | Floor during eDRX                                                | 27                                    | μA   |

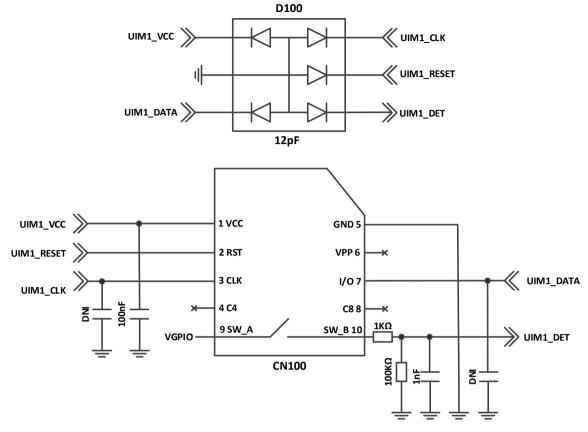

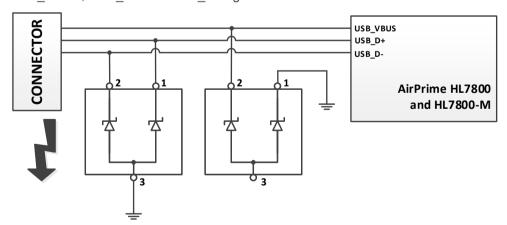

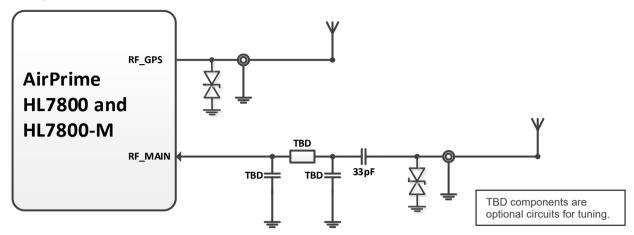

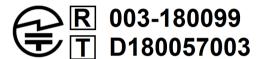

|                      | Hibernate Cycle                   | eDRX cycle (TI-eDRX) = 20.48s and                                | 550°                                  | μΑ   |