# 1x10 W digital input class-D automotive audio amplifier with advanced diagnostics, wide voltage operating range for telematics and e-Call application

QFN32 (exposed pad down)

#### **Features**

- AEC-Q100 qualified

- Integrated 100 dB D/A conversion

- I<sup>2</sup>S and TDM digital input (up to 16CH TDM)

- Selectable input sample rate frequency (8/16/32/44.1/48/96 kHz)

- Wide supply operating range: 3.3 V 18 V

- PWM frequency switching selectable by I<sup>2</sup>C

- 352.8 kHz, 384kHz, 411.6 kHz, 448 kHz

- 2 I<sup>2</sup>C addresses

- MOSFET power outputs

- Typ 10 W 4 Ω at 14.4 V, 1 kHz THD = 1%

- Typ 5 W 8 Ω at 14.4 V, 1 kHz THD = 1%

- Noise: 38 μV A-weighted: 20 kHz

- 8  $\Omega$ , 4  $\Omega$  driving capability

- Input amplitude limiter (configurable through I<sup>2</sup>C)

- I<sup>2</sup>C full configurability and diagnostic

- Startup diagnostic

- Input voltage amplitude limiter function (configurable through I<sup>2</sup>C)

- 4 x Thermal warning

- DC diagnostic

- OCP protection scheme configurable

- Mute time configuration

- Capability to run complete diagnostic in play

- Configurable Clipping Detector

- One of the Thermal Warnings

- Over Current Protection

- Open Load detection

- High voltage mute

- 2 CD/Diag pin

- Integrated ESD and short circuit protection

- · QFN32 wettable flanks

- Tested according to CISPR 25 Class V (Fourth edition)

## **Description**

The FDA803S is the new ST single channel class-D audio amplifier, specifically designed for automotive applications. The FDA803S integrates a 24-bit, 100 dB DAC conversion and PWM class-D output stage with feedback before LC filter. This configuration enables the design of a compact and inexpensive application.

# Product status link FDA803S

| Product summary |                    |               |  |

|-----------------|--------------------|---------------|--|

| Order code      | Package            | Packing       |  |

| FDA803S-6DY     | QFN32              | Tray          |  |

| FDA803S-6DT     | (exp. pad<br>down) | Tape and reel |  |

The FDA803S supports I<sup>2</sup>S and TDM digital bit stream up to 16CH with several sampling frequencies from 8 kHz up to 96 kHz. FDA803S embeds a complete diagnostic in play to support the most demanding OEM requirements in terms of speaker control and system robustness/ reliability.

The FDA803S supports start stop cranking down to 3.3 V and it is available in a very compact and thin QFN 5x5 package. Thus the FDA803S is suitable for any level of automotive application especially e-Call and Telematics.

DB4683 - Rev 3 page 2/15

# 1 Block diagram and pins description

Figure 1. Block diagram D1V8SVR Enable 2 26 — Enable 1 27 — DGSVR VCC1-VCC1-12Cdata 32 - 28 - 30 - 1 - 2 PLL I<sup>2</sup> C interface I2Sclk Digital Core 22 OUT1-19 OUT1+ I2Sws PWM  $I^2 S$ Audio Processing D2A Trans-resistance interface I2SdataIN Power Amplifier Diagnostic 15 A5VSVR 14 AGSVR 16 AVdd 13 SGnd1 25 SGnd2

DB4683 - Rev 3 page 3/15

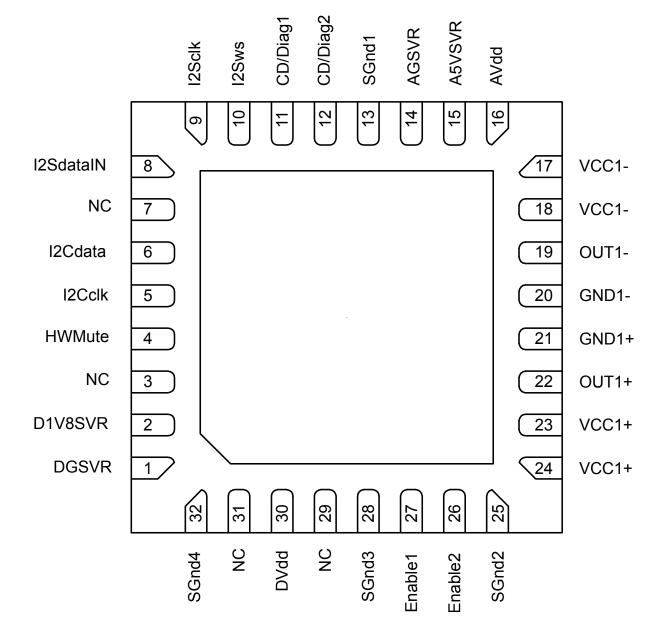

Figure 2. Pin connection diagram (bottom view)

DB4683 - Rev 3 page 4/15

Table 1. Pins description

| N# | Pin                    | Function                                          | Definition         | Internal structure |

|----|------------------------|---------------------------------------------------|--------------------|--------------------|

| 1  | DGSVR                  | Negative digital supply (Internally generated)    | Internal Regulator | -                  |

| 2  | D1V8SVR                | Positive digital supply (Internally generated)    | Internal Regulator | -                  |

| 3  | NC                     | Connected to GND                                  | -                  | -                  |

| 4  | HWMute                 | Hardware mute pin                                 | Input              | -                  |

| 5  | I <sup>2</sup> Cclk    | I <sup>2</sup> C Clock                            | Input              | -                  |

| 6  | I <sup>2</sup> Cdata   | I <sup>2</sup> C Data                             | Input/Output       | Open-Drain         |

| 7  | NC                     | Connected to GND                                  | -                  | -                  |

| 8  | I <sup>2</sup> SdataIN | I <sup>2</sup> S/TDM Data                         | Input              | -                  |

| 9  | l <sup>2</sup> Sclk    | I <sup>2</sup> S/TDM Clock                        | Input              | -                  |

| 10 | I <sup>2</sup> Sws     | I <sup>2</sup> S/TDM Sync                         | Input              | -                  |

| 11 | CD/Diag1               | Clipping detector and diagnostic                  | Output             | Open-Drain         |

| 12 | CD/Diag2               | Clipping detector and diagnostic                  | Output             | Open-Drain         |

| 13 | SGnd1                  | Ground of lower side of circuit, connected to GND | Supply             | -                  |

| 14 | AGSVR                  | Negative digital supply (Internally generated)    | Internal Regulator | -                  |

| 15 | A5VSVR                 | Positive digital supply (Internally generated)    | Internal Regulator | -                  |

| 16 | AVdd                   | Analog supply                                     | Supply             | -                  |

| 17 | VCC1-                  | Channel 1, half bridge minus, Power Supply        | Supply             | -                  |

| 18 | VCC1-                  | Channel 1, half bridge minus, Power Supply        | Supply             | -                  |

| 19 | OUT1-                  | Channel 1, half bridge minus                      | Output             | -                  |

| 20 | GND1-                  | Channel 1, half bridge minus, Power Ground        | Supply             | -                  |

| 21 | GND1+                  | Channel 1, half bridge plus, Power Ground         | Supply             | -                  |

| 22 | OUT1+                  | Channel 1, half bridge plus                       | Output             | -                  |

| 23 | VCC1+                  | Channel 1, half bridge plus, Power Supply         | Supply             | -                  |

| 24 | VCC1+                  | Channel 1, half bridge plus, Power Supply         | Supply             | -                  |

| 25 | SGnd2                  | Ground of upper side of circuit, connected to GND | Supply             | -                  |

| 26 | Enable2                | Enable pin                                        | Input              | -                  |

| 27 | Enable1                | Enable pin                                        | Input              | -                  |

| 28 | SGnd3                  | Ground of upper side of circuit, connected to GND | Supply             | -                  |

| 29 | NC                     | Connected to GND                                  | -                  | -                  |

| 30 | DVdd                   | Digital supply                                    | Supply             | -                  |

| 31 | NC                     | Connected to GND                                  | -                  | -                  |

| 32 | SGnd4                  | Ground of upper side of circuit, connected to GND | Supply             | -                  |

DB4683 - Rev 3 page 5/15

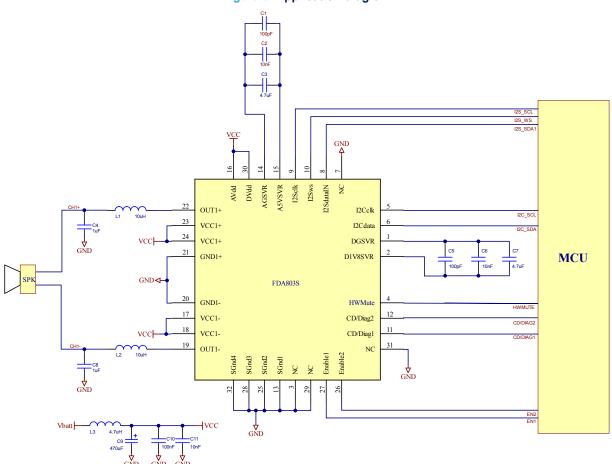

Figure 3. Application diagram

DB4683 - Rev 3 page 6/15

# 2 Electrical specifications

#### 2.1 Thermal data

**Table 2. Thermal resistance**

| Symbol                    | Parameter                                          | Value | Unit |

|---------------------------|----------------------------------------------------|-------|------|

| R <sub>th j-a-2s2pv</sub> | Thermal resistance junction-to-ambient (2s2p+vias) | 32.4  | °C/W |

Note:

- 2s2p is referred to a board with 2 layers dedicated to the signals and 2 layers dedicated to the power signals and supplies.

- from simulation according to Jedec best practice guidelines (JESD51-12) TAMB = 25 °C Infinite Heat Sink.

DB4683 - Rev 3 page 7/15

#### 3 General information

The FDA803S is a fully digital single channel class-D audio amplifier with feedback before LC filter, designed for compact and low-cost Application, such as Telematics and eCall. The feedback before LC architecture has been chosen for allowing smaller components for the demodulator filter, saving cost and space occupation.

The  $I^2S$  interface is used to provide the audio bit stream, with several sampling frequency from 8 kHz up to 96 kHz. The standard format is used for 4 channels applications, while the TDM allows to work up to 16 channels. The  $I^2C$  interface is used to communicate and control the state of the power amplifier, perform the diagnostic and other features.

The FDA803S embeds an internal 24 bits DAC with 100 dB of resolution. Thanks to interpolation and noise shaping, the digital signal processing allows to reach up a good audio performance in a small device area. The internal PLL uses the clock frequency of the bit stream to generate the internal clock for the digital part and PWM for the outputs.

The innovative self-diagnostic algorithm, available also in play, allows the automatic detection of wrong load connections or variation of the load and provides this information through the I<sup>2</sup>C bus to an external microcontroller.

The communication to the microcontroller is improved by two dedicated CD/Diag. All the useful information, such as thermal warnings, input and output offset detection, and some more can be selected by the I<sup>2</sup>C setting and addressed to the one of the CD/Diag pins. Furthermore, one of these pins could be used to synchronize other devices on the platform for better EMC management.

DB4683 - Rev 3 page 8/15

## 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

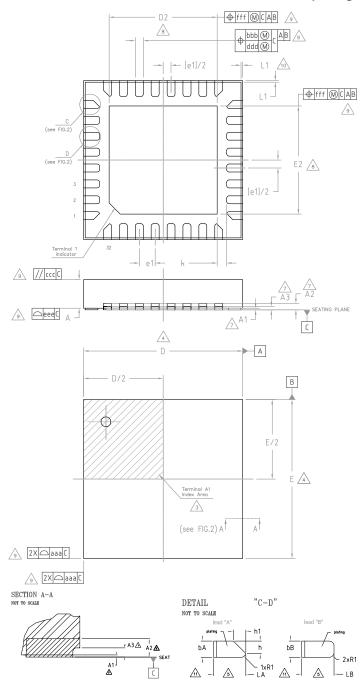

### 4.1 QFN32 5x5x1 (3.5x3.5 32L exp. pad down) package information

Figure 4. QFN 5X5 EP 3.5x3.5 32L WITH WETTABLE FLANKS package outline

DB4683 - Rev 3 page 9/15

Table 3. QFN 5X5 EP 3.5x3.5 32L WITH WETTABLE FLANKS mechanical data

| Symbol | Dimension in mm |                      |      |  |

|--------|-----------------|----------------------|------|--|

| Symbol | Min.            | Тур.                 | Max. |  |

| Α      | 0.80            | 0.90                 | 1.00 |  |

| A1     | 0               | -                    | 0.05 |  |

| A2     | -               | 0.2 REF              | -    |  |

| A3     | 0.10            | -                    | -    |  |

| D      |                 | 5.00 BSC             |      |  |

| D2     | 3.40            | 3.50                 | 3.60 |  |

| E      |                 | 5.00 BSC             | '    |  |

| E2     | 3.40            | 3.50                 | 3.60 |  |

| e1     |                 | 0.50 BSC             |      |  |

| k      | 0.20            | -                    | -    |  |

| L1     | -               | -                    | 0.05 |  |

| La     | 0.40            | 0.50                 | 0.60 |  |

| bA     | 0.20            | 0.25                 | 0.30 |  |

| h      | -               | 0.19 REF             | -    |  |

| h1     | -               | 0.19 REF             | -    |  |

| LB     | 0.45            | 0.50                 | 0.55 |  |

| bB     | 0.20            | 0.25                 | 0.30 |  |

| N      | 32              |                      |      |  |

| R1     | -               | -                    | 0.10 |  |

|        | Tolerance of    | of form and position |      |  |

| aaa    | -               | 0.15                 | -    |  |

| bbb    | -               | 0.10                 | -    |  |

| ccc    | -               | 0.10                 | -    |  |

| ddd    | -               | 0.05                 | -    |  |

| eee    | -               | 0.08                 | -    |  |

| fff    | -               | 0.10                 | -    |  |

DB4683 - Rev 3 page 10/15

# **Revision history**

**Table 4. Document revision history**

| Date        | Version | Changes                                 |

|-------------|---------|-----------------------------------------|

| 07-Mar-2022 | 1       | Initial release.                        |

| 29-Jun-2022 | 2       | Updated Section Features.               |

| 09-Jan-2023 | 3       | Updated Section Device summary.         |

|             |         | Minor text changes in Section Features. |

DB4683 - Rev 3 page 11/15

## **Contents**

| 1   | Bloc                      | k diagram and pins description                              | .3  |

|-----|---------------------------|-------------------------------------------------------------|-----|

| 2   | Electrical specifications |                                                             | .7  |

|     | 2.1                       | Thermal data                                                | . 7 |

| 3   | Gene                      | eral information                                            | .8  |

| 4   | Pack                      | age information                                             | .9  |

|     | 4.1                       | QFN32 5x5x1 (3.5x3.5 32L exp. pad down) package information | . 9 |

| Rev | ision                     | history                                                     | 11  |

## **List of tables**

| Table 1. | Pins description                                            | 5  |

|----------|-------------------------------------------------------------|----|

|          | Thermal resistance                                          |    |

| Table 3. | QFN 5X5 EP 3.5x3.5 32L WITH WETTABLE FLANKS mechanical data | 10 |

| Table 4. | Document revision history                                   | 11 |

DB4683 - Rev 3 page 13/15

# **List of figures**

| Figure 1. | Block diagram                                               | 3 |

|-----------|-------------------------------------------------------------|---|

| Figure 2. | Pin connection diagram (bottom view)                        | 4 |

| Figure 3. | Application diagram                                         | 6 |

| Figure 4. | QFN 5X5 EP 3.5x3.5 32L WITH WETTABLE FLANKS package outline | 9 |

DB4683 - Rev 3 page 14/15

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics - All rights reserved

DB4683 - Rev 3 page 15/15