# OGY Monolithic Fixed-Output 400mA Buck Regulator with Dual 150mA LDOs in 2mm × 2mm DFN

# **FEATURES**

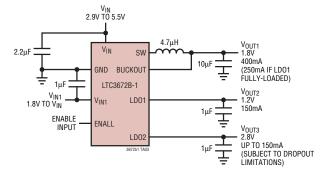

- Triple Output Supply From a Single 2.9V to 5.5V Input

- Buck DC/DC: Fixed 1.8V Output, Up to 400mA

- LD01: Fixed 1.2V Output, Up to 150mA

- LD02: Fixed 2.8V Output, Up to 150mA

- ±2.5% Reference Accuracy

- Constant Frequency 2.25MHz Operation

- Minimum External Component Count

- Current Mode Operation for Excellent Line and Load Transient Response

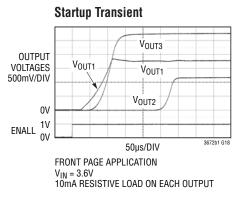

- Internal Soft-Start for Each Output

- Single Enable Pin Turns On/Shuts Down All Three Outputs

- Tiny 2mm × 2mm × 0.75mm DFN Package

# **APPLICATIONS**

- DMB Cellphones

- Handheld Products (PDA, PMP, GPS)

- Multivoltage Power for Digital Logic, I/O, FPGAs, CPLDs. ASICs. CPUs. and RF Chipsets

### DESCRIPTION

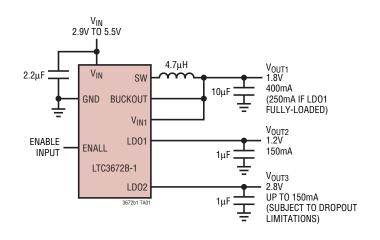

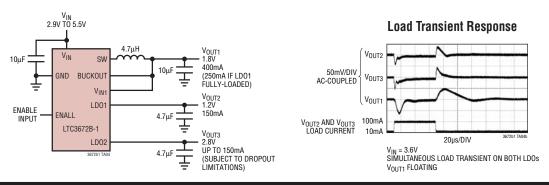

The LTC®3672B-1 is a triple power supply composed of a 400mA synchronous buck regulator and two 150mA low-dropout linear regulators (LDOs), where one of the LDOs can be powered from the buck output to improve efficiency. Constant-frequency 2.25MHz operation is maintained down to very light loads. The input supply range of 2.9V to 5.5V is especially well-suited for single-cell Lithium-lon and Lithium-Polymer applications, and for powering low voltage ASICs from 3.3V or 5V rails.

The LTC3672B-1 regulates 1.8V at the buck output, 1.2V at the LDO1 output, and 2.8V at the LDO2 output. External component count is minimal—all that is needed is a single inductor, an input capacitor, and output capacitors for each of the three outputs. Control loop compensation is internal to the LTC3672B-1.

The LTC3672B-1 is available in a  $2mm \times 2mm \times 0.75mm$  8-Lead DFN package.

# TYPICAL APPLICATION

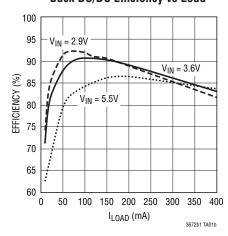

#### **Buck DC/DC Efficiency vs Load**

# **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2, 3)

| V <sub>IN</sub>                        | 0.3V to 6V               |

|----------------------------------------|--------------------------|

| V <sub>IN1</sub> , BUCKOUT, ENALL, SW, |                          |

| LD020.3V to the lesser of $(V_{IN})$   | $_{\rm I}$ + 0.3V) or 6V |

| LD010.3V to the lesser of $(V_{IN1})$  | + 0.3V) or 6V            |

| Junction Temperature                   | 125°C                    |

| Operating Temperature Range            | 40 to 85°C               |

| Storage Temperature Range              | 65 to 125°C              |

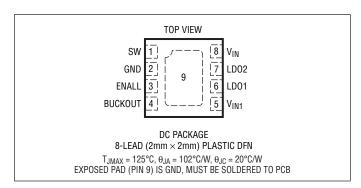

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|--------------------------------|-------------------|

| LTC3672BEDC-1#PBF | LTC3672BEDC-1#TRPBF | LCWH          | 8-Lead (2mm × 2mm) Plastic DFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 3.6V$ , unless otherwise noted.

| SYMBOL                | PARAMETER                                                                      | CONDITIONS                                                         |   | MIN   | TYP  | MAX      | UNITS     |

|-----------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|---|-------|------|----------|-----------|

| V <sub>IN</sub>       | Input Voltage Range                                                            |                                                                    | • | 2.9   |      | 5.5      | V         |

| $V_{UVLO}$            | V <sub>IN</sub> Undervoltage Lockout Threshold                                 | V <sub>IN</sub> Rising                                             |   |       | 1.7  | 2        | V         |

|                       | Undervoltage Lockout Hysteresis                                                |                                                                    |   |       | 12   | 100      | mV        |

| I <sub>Q,VIN</sub>    | V <sub>IN</sub> Quiescent Current<br>All Outputs Enabled, No Load<br>Shutdown  | (Note 4)<br>V <sub>BUCKOUT</sub> = 1.9V<br>V <sub>ENALL</sub> = 0V |   |       | 260  | 400<br>1 | μΑ<br>μΑ  |

| I <sub>Q,VIN1</sub>   | V <sub>IN1</sub> Quiescent Current<br>All Outputs Enabled, No Load<br>Shutdown | $V_{IN1} = 1.8V$ $V_{ENALL} = 0V$                                  |   |       | 2.3  | 5<br>1   | μA<br>μA  |

| $\overline{V_{IL}}$   | ENALL Pin Logic Low Voltage                                                    |                                                                    | • |       |      | 0.4      | V         |

| V <sub>IH</sub>       | ENALL Pin Logic High Voltage                                                   |                                                                    | • | 1.2   |      |          | V         |

| R <sub>ENALL</sub>    | ENALL Pin Pulldown Resistance                                                  |                                                                    |   |       | 5.5  |          | $M\Omega$ |

| Synchronous B         | uck Regulator                                                                  |                                                                    |   |       |      |          |           |

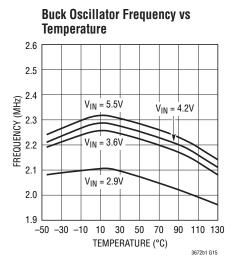

| f <sub>OSC</sub>      | Oscillator Frequency                                                           |                                                                    |   | 1.8   | 2.25 | 2.7      | MHz       |

| V <sub>BUCKOUT</sub>  | Regulated Output Voltage                                                       |                                                                    | • | 1.755 | 1.8  | 1.845    | V         |

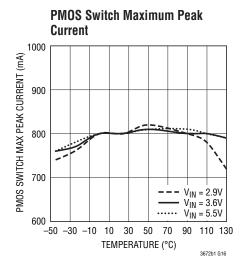

| I <sub>MAXP</sub>     | PMOS Switch Maximum Peak Current (Note 5)                                      |                                                                    |   | 550   | 800  | 1100     | mA        |

| I <sub>OUT,BUCK</sub> | Available Output Current                                                       |                                                                    |   | 400   |      |          | mA        |

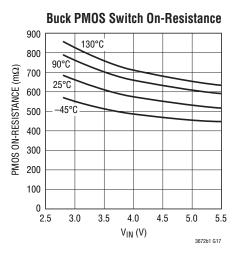

| R <sub>P,BUCK</sub>   | PMOS Switch On-Resistance                                                      |                                                                    |   |       | 0.6  |          | Ω         |

| R <sub>N,BUCK</sub>   | NMOS Switch On-Resistance                                                      |                                                                    |   |       | 0.7  |          | Ω         |

<sup>\*</sup>For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{IN} = 3.6V$ , unless otherwise noted.

| SYMBOL                  | PARAMETER                                                                        | CONDITIONS                                                                                                                                  |   | MIN  | TYP       | MAX  | UNITS        |

|-------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----------|------|--------------|

| R <sub>PD,BUCKOUT</sub> | BUCKOUT Pulldown Resistance in Shutdown                                          | V <sub>ENALL</sub> = 0V                                                                                                                     |   |      | 10        |      | kΩ           |

| R <sub>PD,SW</sub>      | SW Pulldown Resistance in Shutdown                                               | V <sub>ENALL</sub> = 0V                                                                                                                     |   |      | 10        |      | kΩ           |

| t <sub>SS,BUCK</sub>    | Soft-Start Time                                                                  |                                                                                                                                             |   |      | 0.2       |      | ms           |

| LDO Regulator           | 1: V <sub>IN1</sub> = 1.8V Unless Otherwise Noted                                |                                                                                                                                             |   |      |           |      |              |

| $V_{LD01}$              | Regulated Output Voltage                                                         | LD01 Output, I <sub>LD01</sub> = 1mA                                                                                                        | • | 1.17 | 1.2       | 1.23 | V            |

|                         | Line Regulation with Respect to V <sub>IN</sub> with Respect to V <sub>IN1</sub> | I <sub>LD01</sub> = 1mA<br>V <sub>IN</sub> = 3V to 5.5V, V <sub>IN1</sub> = 1.8V<br>V <sub>IN</sub> = 3.6V, V <sub>IN1</sub> = 1.7V to 1.9V |   |      | 0.05<br>1 |      | mV/V<br>mV/V |

|                         | Load Regulation                                                                  | I <sub>LD01</sub> = 1mA to 150mA                                                                                                            |   |      | -0.05     |      | mV/mA        |

|                         | Available Output Current                                                         |                                                                                                                                             |   | 150  |           |      | mA           |

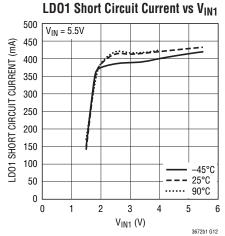

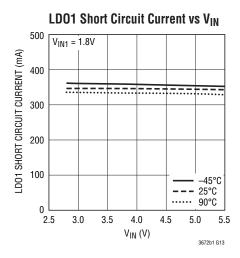

|                         | Short-Circuit Output Current                                                     |                                                                                                                                             |   |      | 347       |      | mA           |

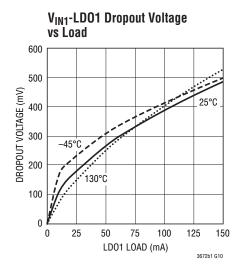

| V <sub>DROP1</sub>      | Dropout Voltage (Note 6)                                                         | I <sub>LD01</sub> = 150mA                                                                                                                   |   |      | 484       | 570  | mV           |

| t <sub>SS,LD01</sub>    | Soft-Start Time                                                                  |                                                                                                                                             |   |      | 0.3       |      | ms           |

| R <sub>PD,LD01</sub>    | Output Pulldown Resistance in Shutdown                                           |                                                                                                                                             |   |      | 10        |      | kΩ           |

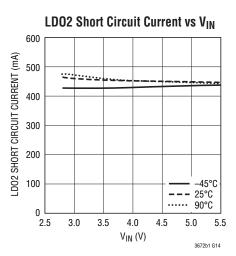

| LDO Regulator           | 2                                                                                |                                                                                                                                             | • |      |           |      |              |

| $V_{LD02}$              | Regulated Output Voltage                                                         | LD02 Output, I <sub>LD02</sub> = 1mA                                                                                                        | • | 2.73 | 2.8       | 2.87 | V            |

|                         | Line Regulation with Respect to V <sub>IN</sub>                                  | I <sub>LD02</sub> = 1mA, V <sub>IN</sub> = 3V to 5.5V                                                                                       |   |      | 1         |      | mV/V         |

|                         | Load Regulation                                                                  | I <sub>LD02</sub> = 1mA to 150mA                                                                                                            |   |      | 0.1       |      | mV/mA        |

|                         | Available Output Current                                                         |                                                                                                                                             |   | 150  |           |      | mA           |

|                         | Short-Circuit Output Current                                                     |                                                                                                                                             |   |      | 453       |      | mA           |

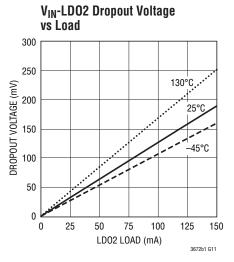

| V <sub>DROP2</sub>      | Dropout Voltage (Note 6)                                                         | I <sub>LD02</sub> = 150mA                                                                                                                   |   |      | 188       | 250  | mV           |

| t <sub>SS,LD02</sub>    | Soft-Start Time                                                                  |                                                                                                                                             |   |      | 0.1       |      | ms           |

| R <sub>PD,LD02</sub>    | Output Pulldown Resistance in Shutdown                                           |                                                                                                                                             |   |      | 10        |      | kΩ           |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3672B-1 is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Dynamic supply current is higher due to the gate charge delivered to the buck regulator's internal MOSFET switches at the switching frequency.

**Note 5:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the specified maximum specified pin current rating may result in device degradation or failure.

**Note 6:** Dropout voltage is the minimum input to output voltage differential needed to maintain regulation at a specified output current. When LDO1 is in dropout, its output voltage will be equal to:  $V_{IN1} - V_{DROP1}$ . When LDO2 is in dropout, its output voltage will be equal to:  $V_{IN} - V_{DROP2}$ .

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C unless otherwise specified.

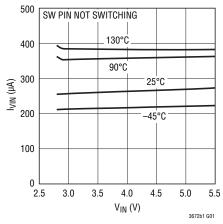

#### V<sub>IN</sub> Quiescent Current vs V<sub>IN</sub> Voltage

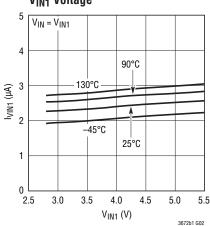

#### V<sub>IN1</sub> Quiescent Current vs V<sub>IN1</sub> Voltage

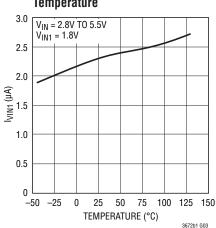

V<sub>IN1</sub> Quiescent Current vs Temperature

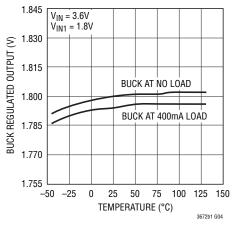

#### Buck Regulated Output vs Temperature

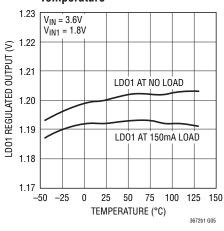

#### LDO1 Regulated Output vs Temperature

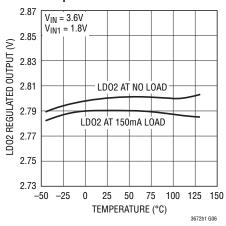

LDO2 Regulated Output vs Temperature

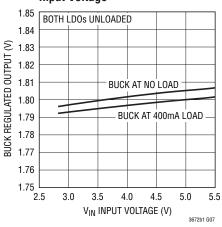

#### Buck Regulated Output vs V<sub>IN</sub> Input Voltage

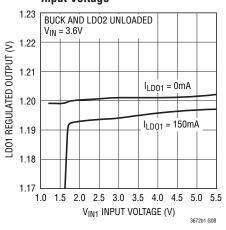

LD01 Regulated Output vs V<sub>IN1</sub>

Input Voltage

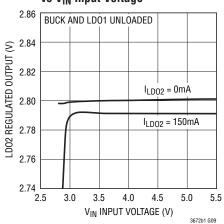

LDO2 Regulated Output Voltage vs V<sub>IN</sub> Input Voltage

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C unless otherwise specified.

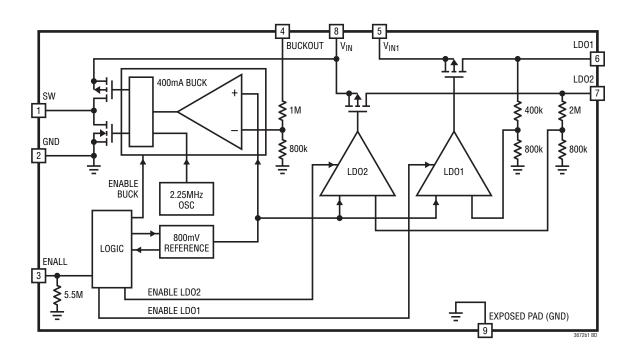

# PIN FUNCTIONS

**SW (Pin 1):** Switch Node Connection to Inductor. This pin connects to the drains of the buck regulator's main PMOS and synchronous NMOS switches.

GND (Pin 2): Ground.

**ENALL (Pin 3):** Enables all three outputs when high, shuts down the IC when low. This is a MOS gate input. An internal  $5.5M\Omega$  resistor pulls this pin to ground.

**BUCKOUT (Pin 4):** Output Voltage Sense Connection for the Buck Regulator.

$V_{IN1}$  (Pin 5): Power Input for the First Low Dropout Linear Regulator, LDO1. This pin may be connected to the buck regulator's output,  $V_{IN}$ , or a voltage not exceeding  $V_{IN}$ .

**LD01 (Pin 6):** Output of the First Low Dropout Linear Regulator. This pin must be bypassed to ground with a 1µF or greater ceramic capacitor.

**LD02 (Pin 7):** Output of the Second Low Dropout Linear Regulator. This pin must be bypassed to ground with a 1µF or greater ceramic capacitor.

$V_{IN}$  (Pin 8): Input Bias Supply for the IC, and Power Input for the Buck Regulator and LD02. This pin should be bypassed to ground with a 2.2 $\mu$ F or greater ceramic capacitor.

**Exposed Pad (Pin 9):** Ground. The Exposed Pad must be soldered to PCB.

# **BLOCK DIAGRAM**

# **OPERATION**

#### INTRODUCTION

The LTC3672B-1 combines a synchronous buck converter with two low dropout linear DC regulators (LDOs) to provide three low voltage outputs from a higher voltage input source. All outputs are enabled and disabled together through the ENALL pin. The output regulation voltages are set during manufacturing to 1.8V nominal for the buck, 1.2V nominal for LDO1, and 2.8V nominal for LDO2. LDO1 may be powered off of the buck output for higher overall efficiency.

For versions of the IC with different output regulation voltages, consult the LTC factory.

#### SYNCHRONOUS BUCK REGULATOR

The synchronous buck uses a constant-frequency current mode architecture, switching at 2.25MHz down to very light loads, and supports no-load operation by skipping cycles. When the input voltage drops very close to or falls below the target output voltage, the buck supports 100% duty cycle operation (low dropout mode). Soft-start circuitry limits inrush current when powering on. Output current is limited in the event of an output short-circuit. The switch node is slew-rate limited to reduce EMI radiation. The buck regulation control-loop compensation is internal to the IC, and requires no external components.

### **Main Control Loop**

An error amplifier monitors the difference between an internal reference voltage and the voltage on the BUCKOUT pin. When the BUCKOUT voltage is below the reference, the error amplifier output voltage increases. When the BUCKOUT voltage exceeds the reference, the error amplifier output voltage decreases.

The error amplifier output controls the peak inductor current through the following mechanism: Paced by a free-running 2.25MHz oscillator, the main P-channel MOSFET switch is turned on at the start of the oscillator cycle. Current flows from the  $V_{IN}$  supply through this PMOS switch, through the inductor via the SW pin, and into the output capacitor and load. When the current reaches the level programmed by the output of the error amplifier, the PMOS is shut off, and the N-channel MOSFET synchronous rectifier turns

on. Energy stored in the inductor discharges into the load through this NMOS. The NMOS turns off at the end of the 2.25MHz cycle, or sooner, if the current through it drops to zero before the end of the cycle.

Through these mechanisms, the error amplifier adjusts the peak inductor current to deliver the required output power to regulate the output voltage as sensed by the BUCKOUT pin. All necessary control-loop compensation is internal to the step-down switching regulator, requiring only a single ceramic output capacitor for stability.

#### Light Load/No-Load Cycle-Skipping

At light loads, the inductor current may reach zero before the end of the oscillator cycle, which will turn off the NMOS synchronous rectifier. In this case, the SW pin goes high impedance and will show damped "ringing". This is known as discontinuous operation, and is normal behavior for a switching regulator. At very light load and no-load conditions, the buck will automatically skip cycles as needed to maintain output regulation.

#### Soft-Start

Soft-start in the buck regulator is accomplished by gradually increasing the maximum allowed peak inductor current over a 200µs period. This allows the output to rise slowly, controlling the inrush current required to charge up the output capacitor. A soft-start cycle occurs whenever the LTC3672B-1 is enabled, or after a fault condition has occurred (thermal shutdown or UVLO).

#### **Switch Slew-Rate Control**

The buck regulator contains new patent pending circuitry to limit the slew rate of the switch node (SW pin). This new circuitry is designed to transition the switch node over a period of a couple nanoseconds, significantly reducing radiated EMI and conducted supply noise while maintaining high efficiency.

#### LOW VIN SUPPLY UNDERVOLTAGE LOCKOUT

An undervoltage lockout (UVLO) circuit shuts down the LTC3672B-1 when V<sub>IN</sub> drops below about 1.7V.

3672B1

### **OPERATION**

## LOW DROPOUT LINEAR REGULATORS (LDOS)

The LTC3672B-1 contains two 150mA fixed-output LDO regulators. LDO1 takes power from the  $V_{IN1}$  pin and regulates a 1.2V output at the LDO1 pin. By connecting  $V_{IN1}$  to the buck regulator's 1.8V output, overall conversion efficiency can be improved, because the bulk of the stepdown will be done by the buck regulator at higher efficiency than what the LDO can do on its own. For example, for the case of deriving a 1.2V output from a 3.6V input (e.g. Lithium-Ion battery nominal voltage), using an LDO to do all of the step-down results in an efficiency of at most

1.2V/3.6V = 33.3%, using the fact that the upper-bound on any linear regulator's efficiency is output voltage divided by input voltage. Feeding the LDO from the output of the buck regulator, with a typical buck efficiency of 85%, raises the ceiling on overall efficiency to 85% • 1.2V/1.8V = 56.6%. This can increase battery life by up to 70%!

LDO2 takes power straight from  $V_{\text{IN}}$  and regulates a 2.8V output at the LDO2 pin.

For stability, each LDO output must be bypassed to ground with a minimum  $1\mu F$  ceramic capacitor.

# APPLICATIONS INFORMATION

#### **BUCK REGULATOR INDUCTOR SELECTION**

Many different sizes and shapes of inductors are available from numerous manufacturers. Choosing the right inductor from such a large selection of devices can be overwhelming, but following a few basic guidelines will make the selection process much simpler.

The buck regulator is designed to work with inductors in the range of  $2.2\mu H$  to  $10\mu H$ . A  $4.7\mu H$  inductor is a good starting point. Larger value inductors reduce ripple current, which improves output ripple voltage. Lower value inductors result in higher ripple current and improved transient response time. To maximize efficiency, choose an inductor with a low DC resistance. Choose an inductor with a DC current rating at least 1.5 times larger than the maximum load current to ensure that the inductor does not saturate during normal operation. If output short circuit is a possible condition, the inductor should be rated to handle the maximum peak current specified for the stepdown converters.

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or Permalloy™ materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. Inductors that are very thin or have a very small volume typically have much higher core and DCR losses, and will not give the best efficiency. The choice of which style inductor to use often depends more on the price vs size, performance, and any radiated EMI requirements than on what the buck regulator needs to operate.

Table 1 shows several inductors that work well with the buck regulator. These inductors offer a good compromise in current rating, DCR and physical size. Consult each manufacturer for detailed information on their entire selection of inductors.

# APPLICATIONS INFORMATION

Table 1. Recommended Inductors for the Buck Regulator

| INDUCTOR TYPE | L<br>(µH)  | MAX I <sub>DC</sub> (A) | MAX DCR<br>(Ω)            | SIZE IN mm<br>(L × W × H)                                                                 | MANUFACTURER                    |

|---------------|------------|-------------------------|---------------------------|-------------------------------------------------------------------------------------------|---------------------------------|

| DB318C        | 4.7<br>3.3 | 1.07<br>1.2             | 0.1<br>0.07               | 3.8 × 3.8 × 1.8<br>3.8 × 3.8 × 1.8                                                        | Toko<br>www.toko.com            |

| D312C         | 4.7<br>3.3 | 0.79<br>0.9             | 0.07<br>0.24<br>0.2       | $3.6 \times 3.6 \times 1.2$<br>$3.6 \times 3.6 \times 1.2$<br>$3.6 \times 3.6 \times 1.2$ | www.toko.com                    |

| DE2812C       | 4.7<br>3.3 | 1.15<br>1.37            | 0.13*<br>0.105*           | $3 \times 2.8 \times 1.2$<br>$3 \times 2.8 \times 1.2$<br>$3 \times 2.8 \times 1.2$       |                                 |

| CDRH3D16      | 4.7<br>3.3 | 0.9<br>1.1              | 0.11<br>0.085             | 4 × 4 × 1.8<br>4 × 4 × 1.8                                                                | Sumida<br>www.sumida.com        |

| CDRH2D11      | 4.7        | 0.5<br>0.6              | 0.17<br>0.123             | $3.2 \times 3.2 \times 1.2$<br>$3.2 \times 3.2 \times 1.2$                                | www.sumua.com                   |

| CLS4D09       | 4.7        | 0.75                    | 0.19                      | 4.9 × 4.9 × 1                                                                             |                                 |

| SD3118        | 4.7<br>3.3 | 1.3<br>1.59             | 0.162<br>0.113            | $3.1 \times 3.1 \times 1.8$<br>$3.1 \times 3.1 \times 1.8$                                | Cooper<br>www.cooperet.com      |

| SD3112        | 4.7        | 0.8<br>0.97             | 0.246<br>0.165            | 3.1 × 3.1 × 1.2<br>3.1 × 3.1 × 1.2                                                        | www.oooperet.com                |

| SD12          | 4.7<br>3.3 | 1.29<br>1.42            | 0.103<br>0.117*<br>0.104* | $5.2 \times 5.2 \times 1.2$                                                               |                                 |

| SD10          | 4.7<br>3.3 | 1.08<br>1.31            | 0.104<br>0.153*<br>0.108* | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                     |                                 |

| LPS3015       | 4.7<br>3.3 | 1.1<br>1.3              | 0.2<br>0.13               | $3 \times 3 \times 1.5$ $3 \times 3 \times 1.5$                                           | Coil Craft<br>www.coilcraft.com |

<sup>\* =</sup> Typical DCR

#### INPUT/OUTPUT CAPACITOR SELECTION

Low ESR (equivalent series resistance) ceramic capacitors should be used to bypass the following pins to ground:  $V_{IN}$ ,  $V_{IN1}$ , the buck output, LDO1, and LDO2. Only X5R or X7R ceramic capacitors should be used because they retain their capacitance over wider voltage and temperature ranges than other ceramic types. A  $10\mu F$  output capacitor is sufficient for the buck regulator output. For good transient response and stability the output capacitor for the buck regulator should retain at least  $4\mu F$  of capacitance over operating temperature and bias voltage. The  $V_{IN}$  pin should be bypassed with a  $2.2\mu F$  capacitor. The LDO1 and LDO2 output pins should be bypassed with a  $1\mu F$  capacitor or greater.  $V_{IN1}$  should be bypassed with a  $1\mu F$  capacitor, which may be omitted if  $V_{IN1}$  is tied to the buck regulator's output capacitor.

Consult with capacitor manufacturers for detailed information on their selection and specifications of ceramic capacitors. Many manufacturers now offer very thin (<1mm tall) ceramic capacitors ideal for use in height-restricted designs. Table 2 shows a list of several ceramic capacitor manufacturers.

**Table 2. Ceramic Capacitor Manufacturers**

| AVX              | www.avxcorp.com |

|------------------|-----------------|

| Murata           | www.murata.com  |

| Taiyo Yuden      | www.t-yuden.com |

| Vishay Siliconix | www.vishay.com  |

| TDK              | www.tdk.com     |

# APPLICATIONS INFORMATION

#### PRINTED CIRCUIT BOARD LAYOUT CONSIDERATIONS

When laying out the printed circuit board, the following list should be followed to ensure proper operation of the LTC3672B-1:

- 1) The Exposed Pad of the package should connect directly to a large ground plane to minimize thermal and electrical impedance.

- 2) The connections from the input supply pins ( $V_{IN}$  and  $V_{IN1}$ ) to their respective decoupling capacitors should be kept as short as possible. The GND side of these capacitors should

- connect directly to the ground plane of the part. The  $V_{IN}$  capacitor provides the AC current to the buck regulator's power MOSFETs and their drivers. It is especially important to minimize PCB trace inductance from this capacitor to the  $V_{IN}$  and GND pins of the LTC3672B-1.

- 3) The switching power trace connecting the SW pin to the inductor should be kept as short as possible to reduce radiated EMI and parasitic coupling.

- 4) The LDO output capacitors should be placed as close to the IC as possible, and connect to the LDO outputs and the GND pin as directly as possible.

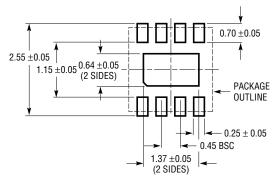

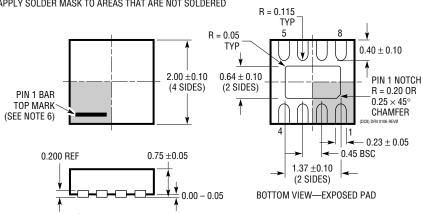

# PACKAGE DESCRIPTION

####

(Reference LTC DWG # 05-08-1719 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

LTC3672B-1 with  $\rm V_{IN1}$  Tied to  $\rm V_{IN},\,V_{OUT1}$  Capable of 400mA Even with  $\rm V_{OUT2}$  and  $\rm V_{OUT3}$  Fully Loaded

2.9V TO 5.5V

2.2µF VIN VIN1 SW

4.7µH VOUT1

1.8V

4.00mA

4.

LTC3672B-1 with  $V_{lN1}$  Tied to an Independent Supply,  $V_{0UT1}$  Capable of 400mA Even with  $V_{0UT2}$  and  $V_{0UT3}$  Fully Loaded

LTC3672B-1 with V<sub>IN1</sub> Tied to Buckout with More LDO Output Capacitance for Improved Transient Response

# **RELATED PARTS**

| PART NUMBER                               | DESCRIPTION                                                                                                     | COMMENTS                                                                                                                               |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| LTC3405/LTC3405A                          | 300mA I <sub>OUT</sub> , 1.5MHz, Synchronous Step-Down DC/DC Converter                                          | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.8V, $I_Q$ = 20 $\mu$ A, $I_{SD}$ <1 $\mu$ A, ThinSOT Package               |

| LTC3406/LTC3406B                          | 600mA I <sub>OUT</sub> , 1.5MHz, Synchronous Step-Down DC/DC Converter                                          | 96% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.6V, $I_Q$ = 20 $\mu$ A, $I_{SD}$ <1 $\mu$ A, ThinSOT Package               |

| LTC3407/LTC3407-2                         | Dual 600mA/800mA I <sub>OUT</sub> , 1.5MHz/2.25MHz, Synchronous<br>Step-Down DC/DC Converter                    | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.6V, $I_Q$ = 40 $\mu$ A, $I_{SD}$ <1 $\mu$ A, MS10E Package                 |

| LTC3410/LTC3410B                          | 300mA I <sub>OUT</sub> , 2.25MHz, Synchronous Step-Down DC/DC Converter                                         | 96% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.8V, $I_Q$ = 26 $\mu$ A, $I_{SD}$ <1 $\mu$ A, SC70 Package                  |

| LTC3411                                   | 1.25A I <sub>OUT</sub> , 4MHz, Synchronous Step-Down DC/DC<br>Converter                                         | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.8V, $I_Q$ = 60 $\mu$ A, $I_{SD}$ <1 $\mu$ A, MS10 Package                  |

| LTC3445                                   | $\mbox{I}^2\mbox{C}$ Controllable 600mA Synchronous Buck Regulator with Two 50mA LDOs in a 4mm $\times$ 4mm QFN | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.85V, $I_Q$ = 360 $\mu$ A, $I_{SD}$ <27 $\mu$ A, 4mm × 4mm QFN Package      |

| LTC3446                                   | Synchronous 1A, 2.25MHz Step-Down DC/DC Regulator with Dual VLDOs                                               | 95% Efficiency, $V_{IN}$ : 2.7V to 5.5V, $V_{OUT(MIN)}$ = 0.4V, $I_Q$ = 140 $\mu$ A, $I_{SD}$ <1 $\mu$ A, 3mm $\times$ 4mm DFN Package |

| LTC3448                                   | 600A I <sub>OUT</sub> , 1.5MHz/2.25MHz, Synchronous<br>Step-Down DC/DC Converter with LDO Mode                  | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.6V, $I_Q$ = 32 $\mu$ A, $I_{SD}$ <1 $\mu$ A, MS10, DFN Packages            |

| LTC3541/LTC3541-1/<br>LTC3541-2/LTC3541-3 | Synchronous 500mA, 2.25MHz Step-Down DC/DC<br>Regulator with a 300mA VLDO in a 3mm × 3mm DFN                    | 95% Efficiency, $V_{IN}$ : 2.7V to 5.5V, $V_{OUT(MIN)}$ = 0.4V, $I_Q$ = 85 $\mu$ A, $I_{SD}$ <1 $\mu$ A, 3mm $\times$ 3mm DFN Package  |

| LTC3547                                   | Dual 300mA I <sub>OUT</sub> , 2.25MHz, Synchronous Step-Down<br>DC/DC Converter                                 | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.6V, $I_Q$ = 40 $\mu$ A, $I_{SD}$ <1 $\mu$ A, DFN-8 Package                 |

| LTC3548/LTC3548-1/<br>LTC3548-2           | Dual 800mA/400mA I <sub>OUT</sub> , 2.25MHz, Synchronous Step-<br>Down DC/DC Converter                          | 95% Efficiency, $V_{IN}$ : 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.6V, $I_Q$ = 40 $\mu$ A, $I_{SD}$ <1 $\mu$ A, MS10, DFN Packages            |

LT 0607 • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2007