ADS127L11 SBAS946C - APRIL 2021 - REVISED SEPTEMBER 2022

# ADS127L11 400-kSPS, Wide-Bandwidth, 24-Bit, Delta-Sigma ADC

### 1 Features

- · Programmable data rate:

- Up to 400 kSPS (wideband filter)

- Up to 1.067 MSPS (low-latency filter)

- Selectable digital filter:

- Wideband or low-latency

- AC accuracy with dc precision:

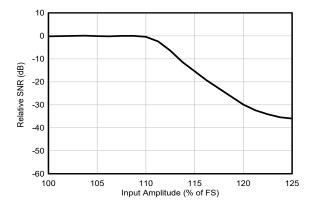

- Dynamic range: 111.5 dB (200 kSPS)

- THD: -120 dB

- INL: 0.9 ppm of FS

- Offset drift: 50 nV/°C

- Gain drift: 0.6 ppm/°C

- Power-scalable architecture:

- High-speed mode: 400 kSPS, 18.6 mW

- Low-speed mode: 50 kSPS, 3.3 mW

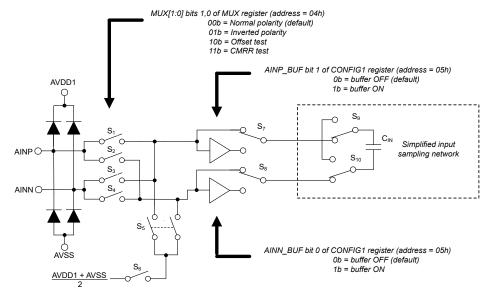

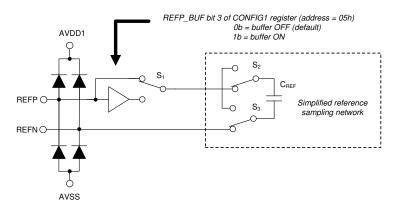

- Input and reference precharge buffers

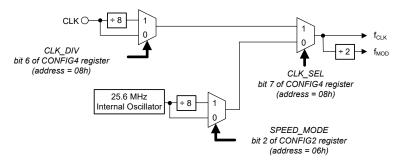

- Internal or external clock

- **Functional Safety-Capable**

- Documentation available to aid functional safety system design

# 2 Applications

- Test and measurement:

- Data acquisition (DAQ)

- Shock and vibration instruments

- Acoustics and dynamic strain gauges

- Factory automation and control:

- Condition monitoring

- Aerospace and defense:

- SONAR

- Medical:

- Electroencephalogram (EEG)

- **Grid Infrastructure:**

- Power quality analyzer

# 3 Description

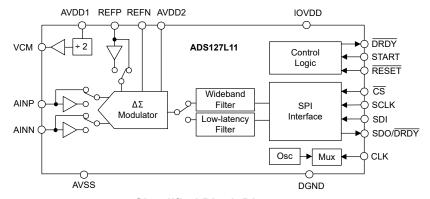

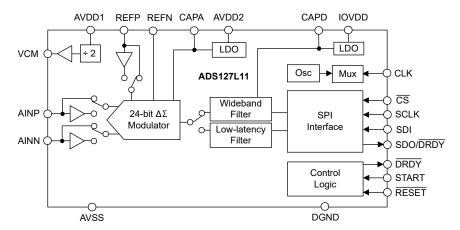

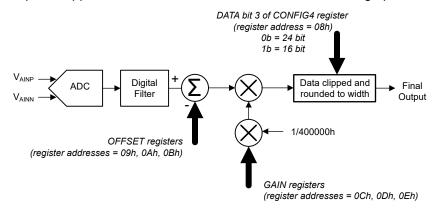

The ADS127L11 is a 24-bit, delta-sigma ( $\Delta\Sigma$ ), analogto-digital converter (ADC) with data rates up to 400 kSPS using the wideband filter and up to 1067 kSPS using the low-latency filter. The device offers an excellent combination of ac performance and dc precision with low power consumption (18.6 mW in high-speed mode).

The device integrates input and reference buffers to reduce signal loading. The low-drift modulator achieves excellent dc precision with low in-band noise for outstanding ac performance. The power-scalable architecture provides two speed modes to optimize data rate, resolution, and power consumption.

The digital filter is configurable for wideband or lowlatency operation, allowing wideband ac performance or data throughput for dc signals to be optimized, all in one device.

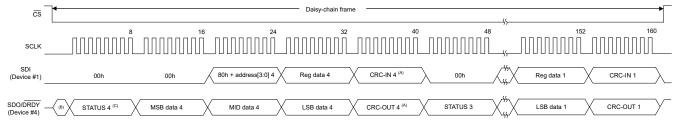

The serial interface features daisy-chain capability to reduce the SPI I/O over an isolation barrier. Input and output data and register settings are validated by a cyclic-redundancy check (CRC) feature to enhance operational reliability.

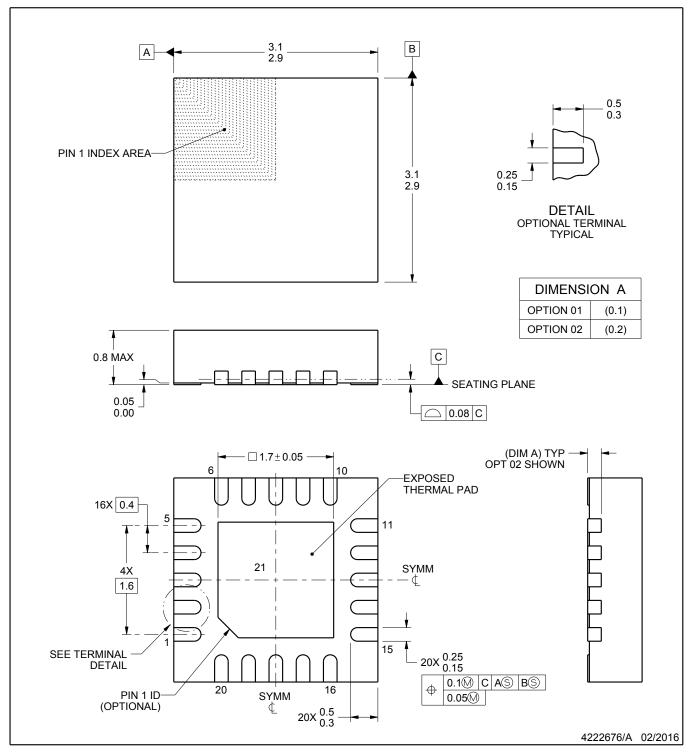

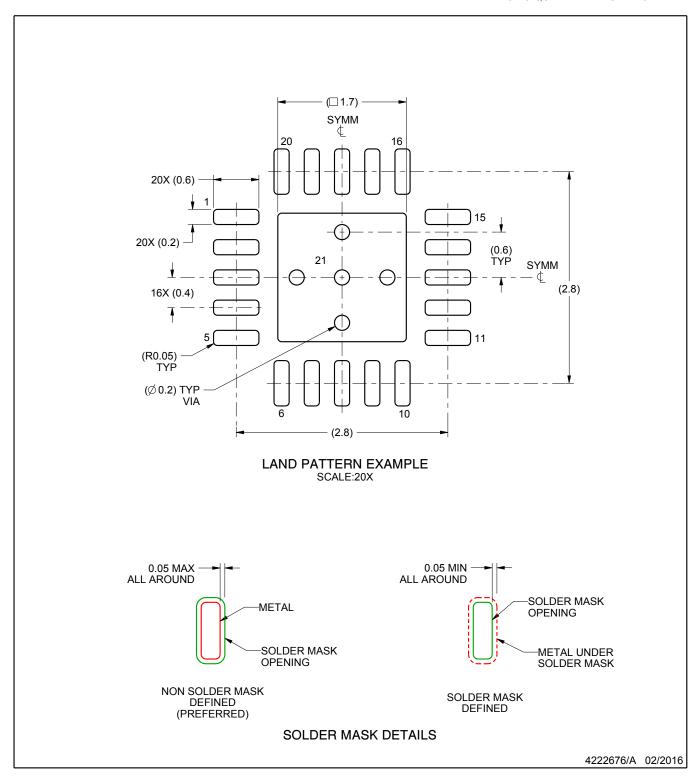

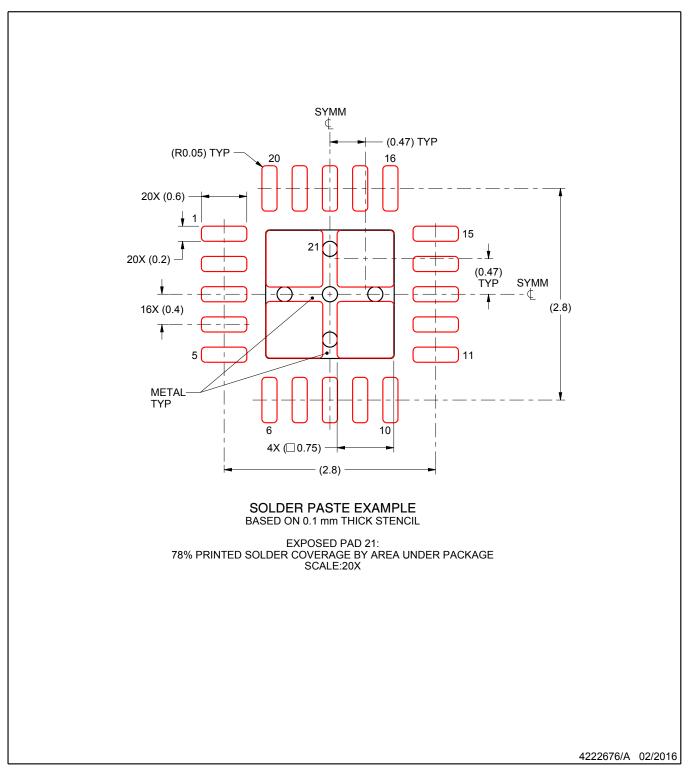

The small 3-mm × 3-mm WQFN and 6.5-mm × 4.4mm TSSOP packages are designed for limited space applications. The device is fully specified for operation over the -40°C to +125°C temperature range.

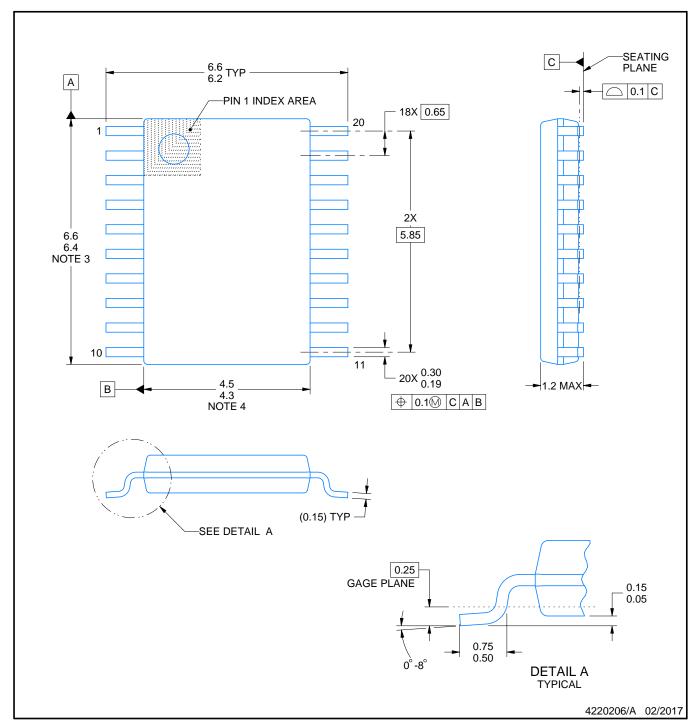

#### Package Information<sup>(1)</sup>

| PART NUMBER | PACKAGE        | BODY SIZE (NOM)   |  |

|-------------|----------------|-------------------|--|

| ADS127I 11  | RUK (WQFN, 20) | 3.00 mm × 3.00 mm |  |

| ADSTZTETT   | PW (TSSOP, 20) | 6.50 mm × 4.40 mm |  |

For all available packages, see the orderable addendum at the end of the data sheet.

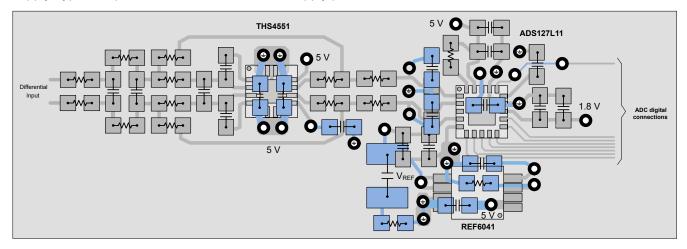

Simplified Block Diagram

# **Table of Contents**

| 1 Features1                                             | 7.9 INL Error Measurement                            | 25 |

|---------------------------------------------------------|------------------------------------------------------|----|

| 2 Applications 1                                        | 7.10 THD Measurement                                 | 25 |

| 3 Description1                                          | 7.11 SFDR Measurement                                | 26 |

| 4 Revision History2                                     | 7.12 Noise Performance                               | 26 |

| 5 Pin Configuration and Functions3                      | 8 Detailed Description                               | 29 |

| 6 Specifications4                                       | 8.1 Overview                                         | 29 |

| 6.1 Absolute Maximum Ratings4                           | 8.2 Functional Block Diagram                         | 29 |

| 6.2 ESD Ratings4                                        | 8.3 Feature Description                              | 30 |

| 6.3 Recommended Operating Conditions5                   | 8.4 Device Functional Modes                          | 44 |

| 6.4 Thermal Information5                                | 8.5 Programming                                      | 49 |

| 6.5 Electrical Characteristics6                         | 8.6 Registers                                        | 60 |

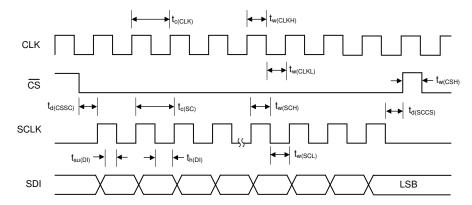

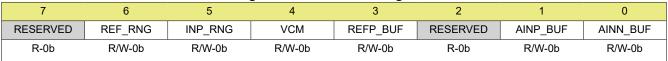

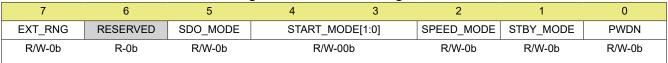

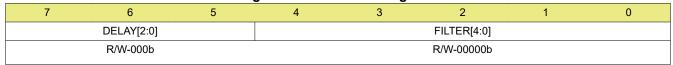

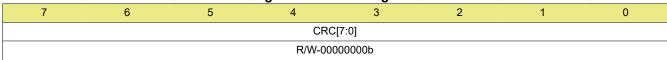

| 6.6 Timing Requirements (1.65 V ≤ IOVDD ≤ 2 V) 10       | 9 Application and Implementation                     | 72 |

| 6.7 Switching Characteristics (1.65 V ≤ IOVDD ≤ 2 V) 10 | 9.1 Application Information                          | 72 |

| 6.8 Timing Requirements (2 V < IOVDD ≤ 5.5 V)11         | 9.2 Typical Application                              | 73 |

| 6.9 Switching Characteristics (2 V < IOVDD ≤ 5.5 V) 11  | 9.3 Power Supply Recommendations                     | 76 |

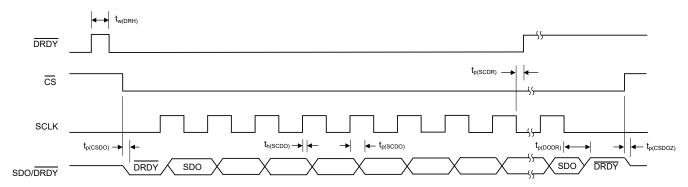

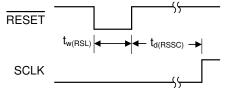

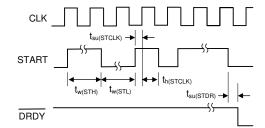

| 6.10 Timing Diagrams12                                  | 9.4 Layout                                           | 77 |

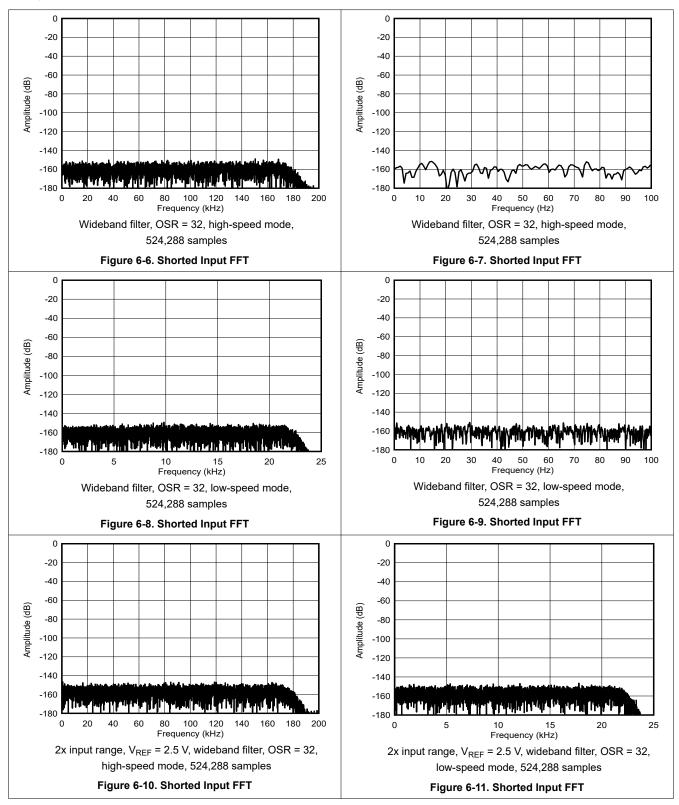

| 6.11 Typical Characteristics13                          | 10 Device and Documentation Support                  |    |

| 7 Parameter Measurement Information23                   | 10.1 Documentation Support                           |    |

| 7.1 Offset Error Measurement23                          | 10.2 Receiving Notification of Documentation Updates | 78 |

| 7.2 Offset Drift Measurement23                          | 10.3 Support Resources                               |    |

| 7.3 Gain Error Measurement23                            | 10.4 Trademarks                                      |    |

| 7.4 Gain Drift Measurement23                            | 10.5 Electrostatic Discharge Caution                 | 78 |

| 7.5 NMRR Measurement23                                  | 10.6 Glossary                                        | 78 |

| 7.6 CMRR Measurement24                                  | 11 Mechanical, Packaging, and Orderable              |    |

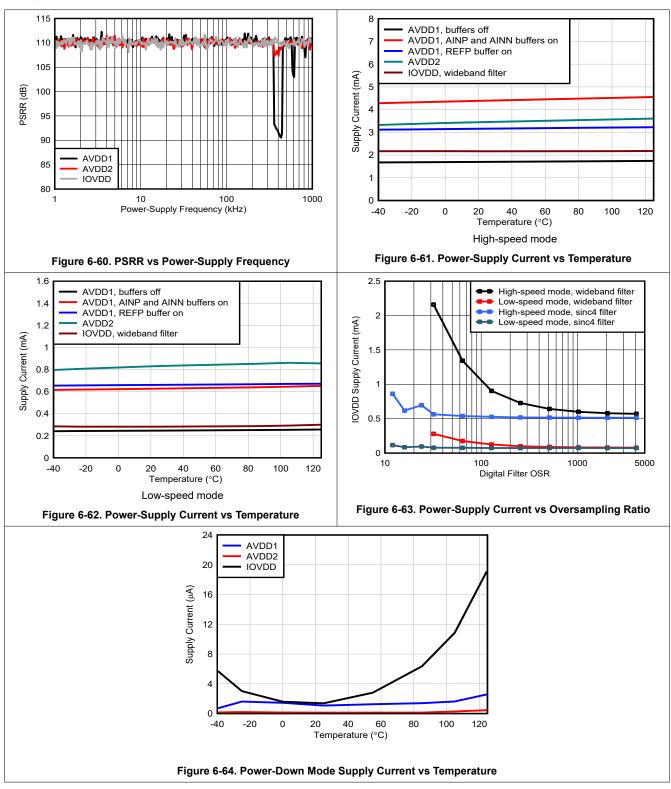

| 7.7 PSRR Measurement24                                  | Information                                          | 78 |

| 7.8 SNR Measurement25                                   |                                                      |    |

|                                                         |                                                      |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision B (April 2022) to Revision C (September 2022)                                             | Page            |

|---|----------------------------------------------------------------------------------------------------------------|-----------------|

| • | Changed RUK (WQFN) package from preview to production data                                                     | 1               |

| • | Changed AVDD1 to DGND specification in Recommended Operating Conditions section                                | 5               |

| • | Changed high-speed mode analog input precharge buffers off current drift specifications in <i>Electrical</i>   |                 |

|   | Characterisics section                                                                                         | 6               |

| • | Changed REFP input precharge buffer on current drift specification in <i>Electrical Characterisics</i> section |                 |

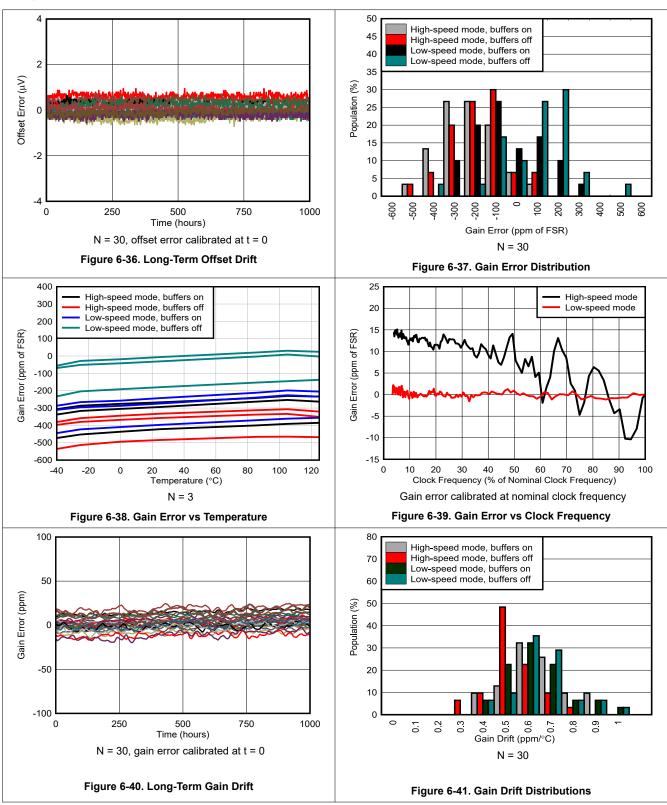

| • | Added Long-Term Offset Drift and Long-Term Gain Drift plots to Typical Characteristics section                 | 13              |

| • | Added second paragraph to Internal Oscillator section                                                          | 34              |

| • | Added footnote to Wideband Filter Characteristics table in Wideband Filter section                             | 35              |

| • | Added footnote to Sinc4 Filter Characteristics table in Sinc4 Filter section                                   | 38              |

| • | Added footnote to Sinc4 + Sinc1 Filter Characteristics table in Sinc4 + Sinc1 Filter section                   | 39              |

| • | Changed Digital Supply Threshold and Analog Supply Threshold figures in Power-On Reset section                 | 43              |

| С | hanges from Revision A (October 2021) to Revision B (April 2022)                                               | Page            |

| • | Changed INL specification in <i>Electrical Characteristics</i> section                                         | 6               |

| • | Changed SPI CRC section                                                                                        | <mark>50</mark> |

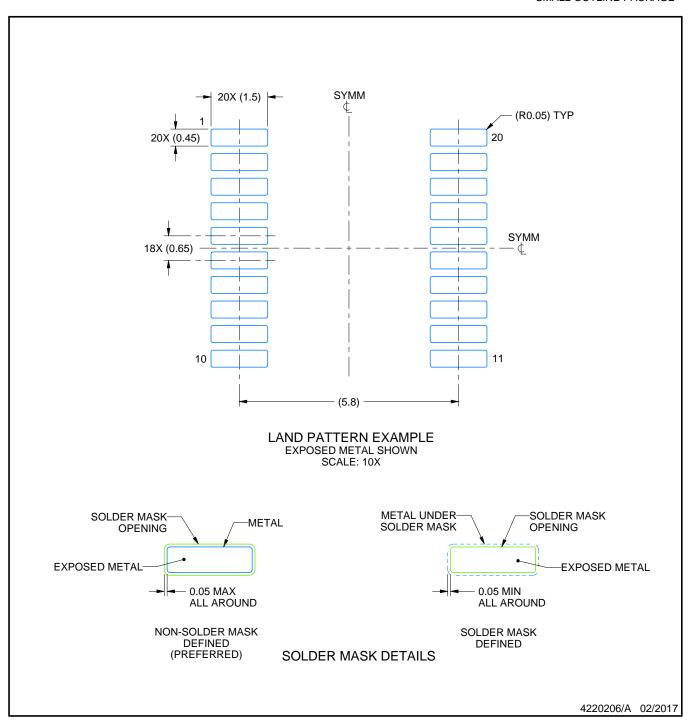

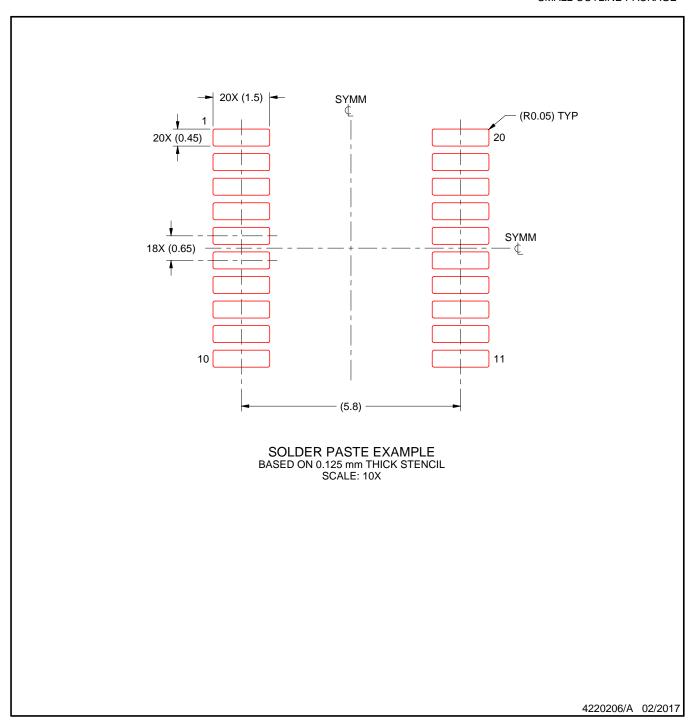

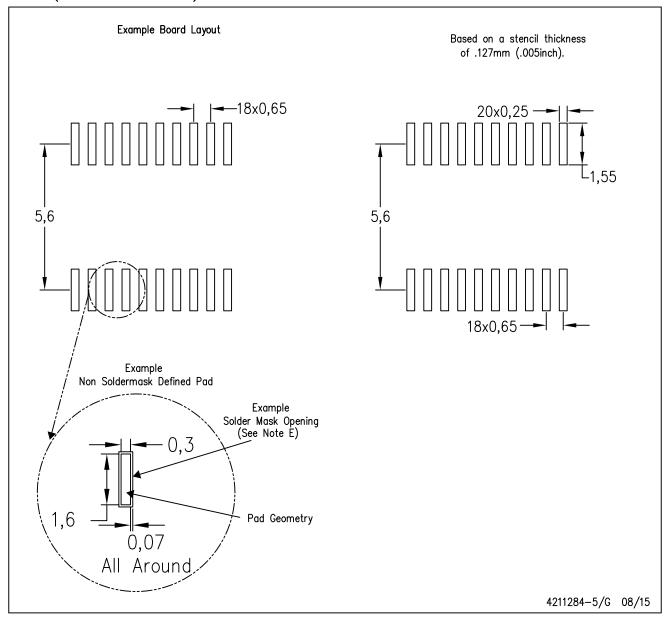

# **5 Pin Configuration and Functions**

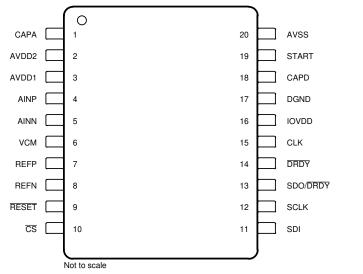

Figure 5-1. PW Package, 20-Pin TSSOP (Top View)

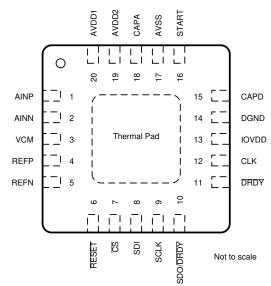

Figure 5-2. RUK Package, 20-Pin WQFN (Top View)

Table 5-1. Pin Functions

| NAME        | PIN   | NO.  | 1/0            | DESCRIPTION                                                                                                                                    |  |

|-------------|-------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | TSSOP | WQFN | l/O            | DESCRIPTION                                                                                                                                    |  |

| AINN        | 5     | 2    | Analog input   | Negative analog input; see the <i>Analog Input</i> section for details  Positive analog input; see the <i>Analog Input</i> section for details |  |

| AINP        | 4     | 1    | Analog input   | Positive analog input; see the <i>Analog Input</i> section for details                                                                         |  |

| AVDD1       | 3     | 20   | Analog Supply  | Positive analog supply 1; see the <i>Power Supplies</i> section for details                                                                    |  |

| AVDD2       | 2     | 19   | Analog Supply  | Positive analog supply 2; see the <i>Power Supplies</i> section for details                                                                    |  |

| AVSS        | 20    | 17   | Analog Supply  | Negative analog supply; see the <i>Power Supplies</i> section for details                                                                      |  |

| CAPA        | 1     | 18   | Analog output  | Analog voltage regulator output capacitor bypass                                                                                               |  |

| CAPD        | 18    | 15   | Analog output  | Digital voltage regulator output capacitor bypass                                                                                              |  |

| CLK         | 15    | 12   | Digital input  | Clock input; see the <i>Clock Operation</i> section for details                                                                                |  |

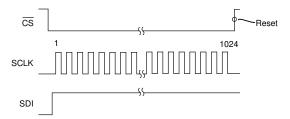

| CS          | 10    | 7    | Digital input  | Chip select, active low; see the Chip Select section for details                                                                               |  |

| DGND        | 17    | 14   | Ground         | Digital ground                                                                                                                                 |  |

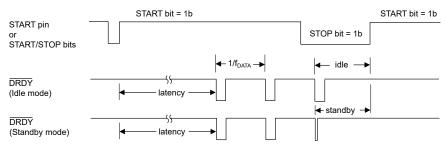

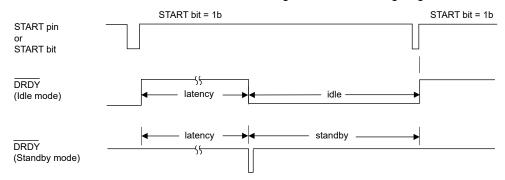

| DRDY        | 14    | 11   | Digital output | Data ready, active low; see the Data Ready section for details                                                                                 |  |

| IOVDD       | 16    | 13   | Digital Supply | I/O supply voltage; see the <i>Power Supplies</i> section for details                                                                          |  |

| REFN        | 8     | 5    | Analog input   | Negative reference input; see the <i>Reference Voltage</i> section for details                                                                 |  |

| REFP        | 7     | 4    | Analog input   | Positive reference input; see the Reference Voltage section for details                                                                        |  |

| RESET       | 9     | 6    | Digital input  | Reset, active low; see the <i>Reset</i> section for details                                                                                    |  |

| SCLK        | 12    | 9    | Digital input  | Serial data clock; see the Serial Clock section for details                                                                                    |  |

| SDI         | 11    | 8    | Digital input  | Serial data input; see the Serial Data Input section for details                                                                               |  |

| SDO/DRDY    | 13    | 10   | Digital output | Serial data output and data ready (optional); see the SDO/DRDY section for details                                                             |  |

| START       | 19    | 16   | Digital input  | Conversion start; see the Synchronization section for details                                                                                  |  |

| VCM         | 6     | 3    | Analog output  | Common-mode voltage buffered output; see the VCM Output Voltage section for details                                                            |  |

| Thermal Pad | _     | Pad  | _              | Thermal power pad; connect to AVSS                                                                                                             |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted) (1)

|                              | 1 3 ( ,                                         | MIN        | MAX         | UNIT |

|------------------------------|-------------------------------------------------|------------|-------------|------|

|                              | AVDD1 to AVSS                                   | -0.3       | 6.5         |      |

|                              | AVDD2 to AVSS                                   | -0.3       | 6.5         |      |

| Power supply voltage         | AVSS to DGND                                    | -3         | 0.3         | V    |

|                              | IOVDD to DGND                                   | -0.3       | 6.5         |      |

|                              | IOVDD to AVSS                                   |            | 8.5         |      |

| Analog input voltage         | AINP, AINN, REFP, REFN                          | AVSS - 0.3 | AVDD1 + 0.3 | V    |

|                              | CAPA                                            | AVSS       | 1.65        |      |

| Analog output voltage        | CAPD                                            | DGND       | 1.65        | V    |

|                              | VCM                                             | AVSS       | AVDD1       |      |

| Digital input/output voltage | SDO/DRDY, DRDY, START                           | DGND - 0.3 | IOVDD + 0.3 | V    |

| Digital input/output voltage | CS, SCLK, SDI, RESET, CLK                       | DGND - 0.3 | 6.5         | V    |

| Input current                | Continuous, any pin except power-supply pins(2) | -10        | 10          | mA   |

| Temperature                  | Junction, T <sub>J</sub>                        |            | 150         | °C   |

| remperature                  | Storage, T <sub>stg</sub>                       | -65        | 150         | C    |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) Analog input pins AINP, AINN, REFP, and REFN are diode-clamped to AVDD1 and AVSS. Limit the input current to 10 mA in the event the analog input voltage exceeds AVDD1 + 0.3 V or AVSS 0.3 V. Digital input pin START and digital output pins SDO/DRDY and DRDY are diode-clamped to IOVDD and DGND. Digital input pins CS, SCLK, SDI, RESET and CLK are diode-clamped to DGND. Limit the input current to 10 mA in the event the digital input voltage exceeds IOVDD + 0.3 V (for effected pins) or exceeds DGND 0.3 V.

## 6.2 ESD Ratings

|       |                                            |                                                                       | VALUE | UNIT  |

|-------|--------------------------------------------|-----------------------------------------------------------------------|-------|-------|

| V     | V <sub>(ESD)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | 2000  | V     |

| (ESD) |                                            | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 1000  | \ \ \ |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# **6.3 Recommended Operating Conditions**

over operating ambient temperature range (unless otherwise noted)

|                     |                                                                                    |                                        | MIN                 | NOM   | MAX                | UNIT |

|---------------------|------------------------------------------------------------------------------------|----------------------------------------|---------------------|-------|--------------------|------|

| POWER               | SUPPLY                                                                             |                                        |                     |       |                    |      |

|                     |                                                                                    | AVDD1 to AVSS, high-speed mode         | 4.5                 |       | 5.5                |      |

|                     |                                                                                    | AVDD1 to AVSS, low-speed mode          | 2.85                |       | 5.5                | V    |

|                     |                                                                                    | AVDD1 to DGND                          | 1.65                |       |                    |      |

|                     | Analog power supply                                                                | Absolute ratio of AVSS / AVDD1 to DGND |                     |       | 1.2                | V/V  |

|                     |                                                                                    | AVDD2 to AVSS                          | 1.74                |       | 5.5                | .,   |

|                     |                                                                                    | AVSS to DGND                           | -2.75               |       | 0                  | V    |

|                     | Digital power supply                                                               | IOVDD to DGND                          | 1.65                |       | 5.5                | V    |

| ANALO               | G INPUTS                                                                           |                                        |                     |       |                    |      |

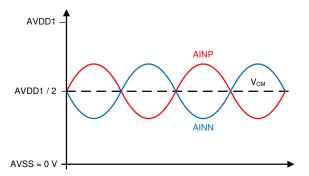

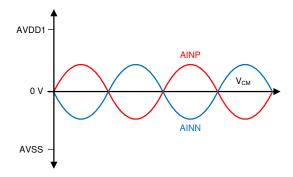

| V <sub>AINP</sub> , | AL 1.1. 1.11                                                                       | Precharge buffer off                   | AVSS - 0.05         |       | AVDD1 + 0.05       | .,   |

| V <sub>AINN</sub>   | Absolute input voltage                                                             | Precharge buffer on                    | AVSS + 0.1          |       | AVDD1 – 0.1        | V    |

| V <sub>IN</sub>     | Differential input voltage V <sub>IN</sub> = V <sub>AINP</sub> - V <sub>AINN</sub> | 1x input range                         | -V <sub>REF</sub>   |       | $V_{REF}$          | V    |

|                     |                                                                                    | 2x input range                         | −2·V <sub>REF</sub> |       | 2·V <sub>REF</sub> | V    |

| VOLTAC              | SE REFERENCE INPUTS                                                                |                                        |                     |       |                    |      |

| V                   | Differential reference voltage                                                     | Low-reference range 0.5                |                     | 2.5   | 2.75               |      |

| $V_{REF}$           | $V_{REF} = V_{REFP} - V_{REFN}$                                                    | High-reference range                   | 1                   | 4.096 | AVDD1 – AVSS       | V    |

| V <sub>REFN</sub>   | Negative reference voltage                                                         |                                        | AVSS - 0.05         |       |                    | V    |

| .,                  | D 37 6 11                                                                          | REFP precharge buffer off              |                     |       | AVDD1 + 0.05       | v    |

| $V_{REFP}$          | Positive reference voltage                                                         | REFP precharge buffer on               |                     |       | AVDD1 – 0.7        | V    |

| EXTER               | NAL CLOCK SOURCE                                                                   |                                        |                     |       |                    |      |

| ,                   | 01.1.6                                                                             | High-speed mode                        | 0.5                 | 25.6  | 26.2               |      |

| f <sub>CLK</sub>    | Clock frequency                                                                    | Low-speed mode                         | 0.5                 | 3.2   | 3.28               | MHz  |

| DIGITAL             | INPUTS                                                                             |                                        |                     |       |                    | ı    |

| V <sub>IL</sub>     | Logic input voltage, low                                                           |                                        | DGND                |       | 0.3·IOVDD          | V    |

| V <sub>IH</sub>     | Logic input voltage, high                                                          |                                        | 0.7·IOVDD           |       | IOVDD              | V    |

| TEMPE               | RATURE RANGE                                                                       |                                        |                     |       |                    |      |

| T <sub>A</sub>      | Operating ambient temperature                                                      |                                        | -45                 |       | 125                | °C   |

# **6.4 Thermal Information**

|                       |                                              | ADS127L11  |            |      |  |

|-----------------------|----------------------------------------------|------------|------------|------|--|

|                       | THERMAL METRIC (1)                           | WQFN (RUK) | TSSOP (PW) | UNIT |  |

|                       |                                              | 20 PINS    | 20 PINS    |      |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 46.0       | 92.9       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 43.9       | 32.9       | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 19.9       | 44.4       | °C/W |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.7        | 2.2        | °C/W |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 19.9       | 43.9       | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.1        | n/a        | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at AVDD1 = 5 V, AVDD2 = 1.8 V to 5 V, AVSS = 0 V, IOVDD = 1.8 V,  $V_{IN} = 0$  V,  $V_{CM} = 2.5$  V,  $V_{REFP} = 4.096$  V,  $V_{REFN} = 0$  V, high-reference range, 1x input range,  $f_{CLK} = 25.6$  MHz (high-speed mode),  $f_{CLK} = 3.2$  MHz (low-speed mode), input precharge buffers on, and reference precharge buffer on (unless otherwise noted)

|                   | PARAMETER                                       | TEST CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ONDITIONS                     | MIN          | TYP                 | MAX  | UNIT    |

|-------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|---------------------|------|---------|

| ANALO             | G INPUTS, HIGH-SPEED MODE                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |                     |      |         |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 95                  |      |         |

|                   | Input current, differential input voltage       | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x input range                 |              | 47                  |      | μA/V    |

|                   | unierentiai iriput voitage                      | Precharge buffers off Precharge buffers off Precharge buffers off, 2x in Precharge buffers off Precharge buffers off Precharge buffers off Precharge buffers off Precharge buffers off, 2x in Precharge buffers off |                               |              | ±3                  |      | μA      |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 3                   |      |         |

|                   | Input current drift, differential input voltage | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x input range                 |              | 1.5                 |      | nA/V/°( |

|                   | unierentiai iriput voitage                      | Precharge buffers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |              | 5                   |      | nA/°C   |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 5                   |      |         |

|                   | Input current,                                  | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x input range                 |              | 2.5                 |      | μA/V    |

|                   | common-mode input voltage                       | Precharge buffers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |              | ±3                  |      | μΑ      |

| ANALO             | G INPUTS, LOW-SPEED MODE                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |                     |      |         |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 12                  |      |         |

|                   | Input current, differential input voltage       | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x input range                 |              | 6                   |      | μA/V    |

|                   | unierentiai iriput voitage                      | Precharge buffers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |              | ±0.4                |      | μA      |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 1                   |      |         |

|                   | Input current drift, differential input voltage | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | c input range                 |              | 0.5                 |      | nA/V/°( |

|                   | unierentiai iriput voitage                      | Precharge buffers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |              | 0.2                 |      | nA/°C   |

|                   |                                                 | Precharge buffers off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |              | 0.6                 |      |         |

|                   | Input current,                                  | Precharge buffers off, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x input range                 |              | 0.3                 |      | μA/V    |

|                   | common-mode input voltage                       | Precharge buffers on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ·                             |              | ±0.4                |      | μA      |

| DC PER            | FORMANCE                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |                     |      |         |

|                   | Resolution                                      | OSR ≥ 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |              | 24                  |      | Bits    |

|                   | Noise                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               | See Noise Pe | erformance for deta | ails |         |

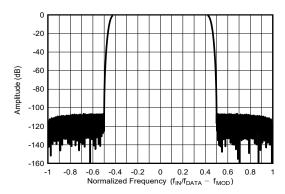

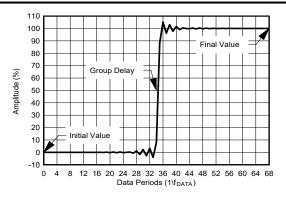

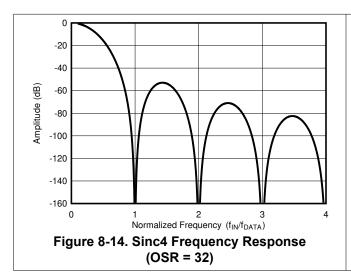

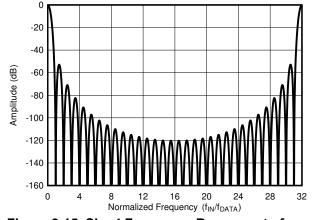

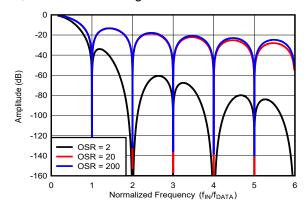

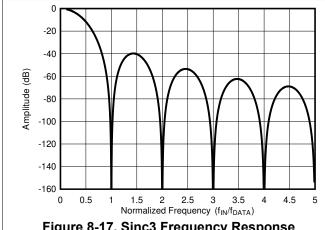

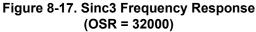

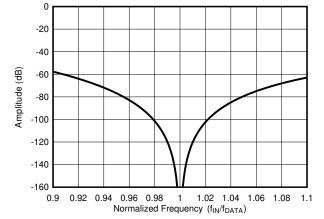

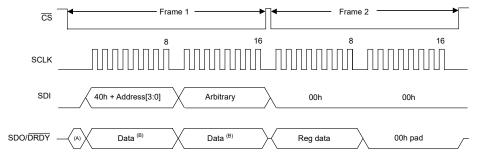

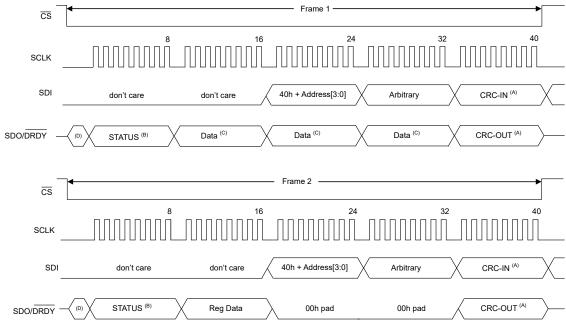

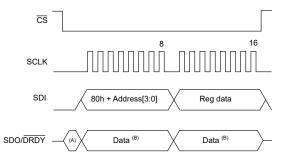

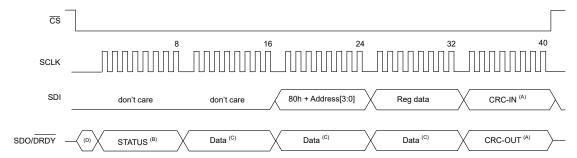

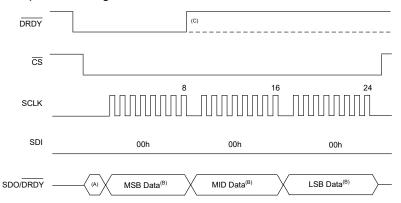

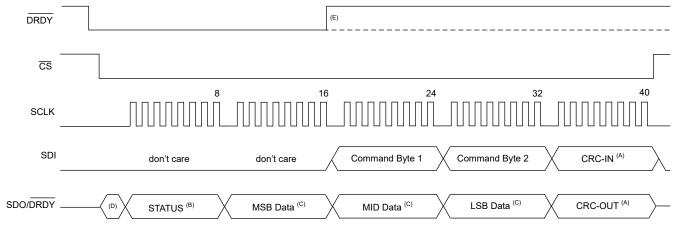

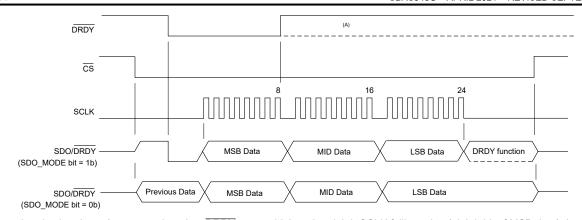

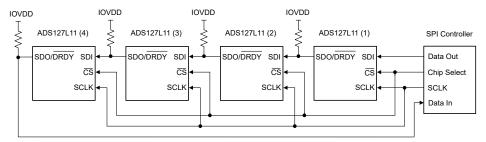

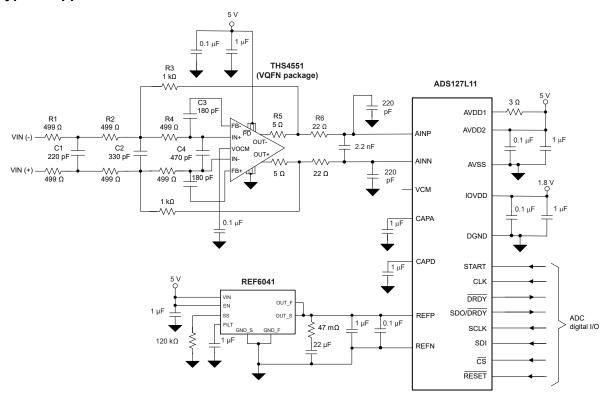

|                   |                                                 | High-speed mode, low-l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | atency filter                 | 0.08         |                     | 1067 |         |